# 8293 GPIB TRANSCEIVER

- Nine Open-collector or Three-state Line Drivers

- 48 mA Sink Current Capability on Each Line Driver

- Nine Schmitt-type Line Receivers

- High Capacitance Load Drive Capability

- Single 5V Power Supply

- 28-Pin Package

- Low Power HMOS Design

- On-chip Decoder for Mode Configuration

- Power Up/Power Down Protection to Prevent Disrupting the IEEE Bus

- Connects with the 8291A and 8292 to Form an IEEE Standard 488 Interface Talker/Listener/Controller with no Additional Components

- Only Two 8293's Required per GPIB Interface

- On-Chip IEEE-488 Bus Terminations

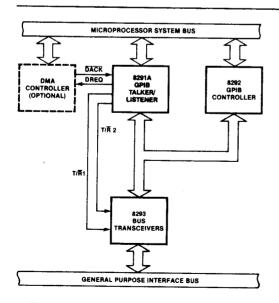

The Intel® 8293 GPIB Transceiver is a high-current, non-inverting buffer chip designed to interface the 8291A GPIB Talker/Listener, or the 8291A/8292 GPIB Talker/Listener/Controller combination, to the IEEE Standard 488-1978 Instrumentation Interface Bus. Each GPIB interface would contain two 8293 Bus Transceivers. In addition, the 8293 can also be used as a general-purpose bus driver.

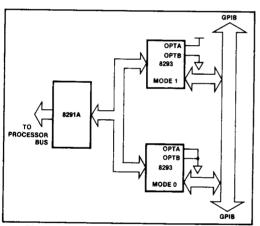

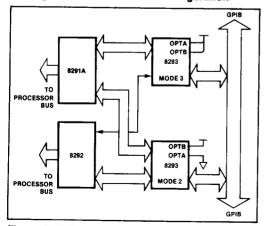

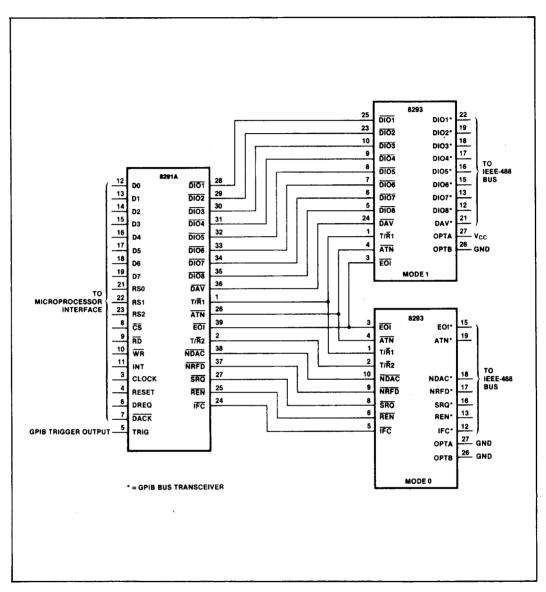

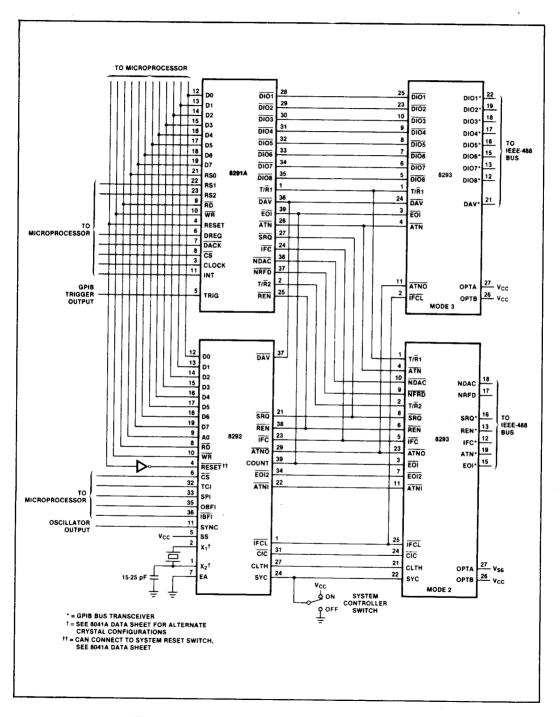

Figure 1. 8291A, 8292, 8293 Block Diagram

Figure 2. Pin Configuration

Table 1. Pin Description

| Symbol           | Pin No.                     | Туре | Name and Function                                                                                                                                                                                                             |

|------------------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS1-<br>BUS9    | 12, 13,<br>15–19,<br>21, 22 | 1/0  | GPIB Lines, GPIB Side: These are the IEEE-488 bus interface driver/receivers, or TTL-compatible inputs on the 8291A/8292 side depending on the mode used. Their use is programmed by the two mode select pins, OPTA and OPTB. |

| DATA1-<br>DATA10 | 5–11,<br>23–25              | 1/0  | GPIB Lines, 8291A/92 Side: These are the pins to be connected to the 8291A and 8292 to interface with the GPIB. Their use is programmed by the two mode select pins, OPTA and OPTB. All these pins are TTL compatible.        |

| T/R1             | 1                           |      | Transmit Receive 1: This pin controls the direction for NDAC, NRFD, DAV, and DIO1-DIO8. Input is TTL compatible.                                                                                                              |

| T/R2             | 2                           | 1    | Transmit Receive 2: This pin controls the direction for EOI. Input is TTL compatible.                                                                                                                                         |

| Symbol       | Pin No.  | Type | Name and Function                                                                                                                                                                                                                                               |

|--------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒΟΙ          | 3        | 1/0  | End Or Identify: This pin indicates the end of a multiple byte transfer or, in conjunction with ATN, addresses the device during a polling sequence. It connects to the 8291A and is switched between transmit and receive by T/R2. This pin is TTL compatible. |

| ATN          | - 4      | 0    | Attention: This pin is used by the 8291A to monitor the GPIB ATN control line. It specifies how data on the DIO lines is to be interpreted. This output is TTL compatible.                                                                                      |

| OPTA<br>OPTB | 27<br>26 | 1 1  | Mode Select: These two pins are to control the function of the 8293. A truth table of how they program the various modes is in Table 2.                                                                                                                         |

| VCC          | 28       | P.S. | Voltage: Positive power supply (5V ± 10%).                                                                                                                                                                                                                      |

| GND          | 14, 20   | P.S. | Ground: Circuit ground.                                                                                                                                                                                                                                         |

Table 2. 8293 Mode Selection Pin Mapping

|          |         | IEEE Implementation Name |        |        |        |  |  |  |

|----------|---------|--------------------------|--------|--------|--------|--|--|--|

| Pin Name | Pin No. | Mode 0                   | Mode 1 | Mode 2 | Mode 3 |  |  |  |

| OPTA     | 27      | 0                        | 1      | 0      | 1      |  |  |  |

| ОРТВ     | 26      | 0                        | 0      | 1      | 1      |  |  |  |

| DATA1    | 5       | IFC                      | DIO8   | IFC    | DIO8   |  |  |  |

|          | 12      | IFC*                     | DIO8*  | IFC*   | DIO8*  |  |  |  |

| BUS1     | 6       | REN                      | DIO7   | REN    | DI07   |  |  |  |

| DATA2    |         | REN*                     | DIO7*  | REN*   | DI07*  |  |  |  |

| BUS2     | 13<br>7 | NC NC                    | DIO6   | EOI2   | DIO6   |  |  |  |

| DATA3    |         | EOI*                     | DIO6*  | EOI.   | DIO6*  |  |  |  |

| BUS3     | 15      |                          | DIO5   | SRQ    | DIO5   |  |  |  |

| DATA4    | 8       | SRQ                      | DIO5*  | SRQ*   | DIO5*  |  |  |  |

| BUS4     | 16      | SRQ*                     |        | NRFD   | DIO4   |  |  |  |

| DATA5    | 9       | NRFD                     | DIO4   |        | DIO4*  |  |  |  |

| BUS5     | 17      | NRFD*                    | DIO4*  | NRFD*  |        |  |  |  |

| DATA6    | 10      | NDAC                     | DIO3   | NDAC   | DIO3   |  |  |  |

| BUS6     | 18      | NDAC*                    | DIO3*  | NDAC*  | DIO3.  |  |  |  |

| DATA7    | 11      | T/RIO1                   | NC_    | ATNI   | ATNO   |  |  |  |

| DATA8    | 23      | T/RIO2                   | DIO2   | ATNO   | DIO2   |  |  |  |

| BUS7     | 19      | ATN*                     | DIO2*  | ATN*   | DIO2*  |  |  |  |

| DATA9    | 24      | GIO1                     | DAV    | CIC    | DAV    |  |  |  |

| BUS8     | 21      | GIO1*                    | DAV*   | CLTH   | DAV*   |  |  |  |

| DATA10   | 25      | GIO2                     | DIO1   | IFCL   | DIO1   |  |  |  |

| BUS9     | 22      | GIO2*                    | DIO1*  | SYC    | DIO1*  |  |  |  |

| 5505     |         |                          |        |        |        |  |  |  |

| T/R1     | 1       | T/R1                     | T/R1   | T/R1   | T/R1   |  |  |  |

| T/R2     |         | T/R2                     | NC     | T/Ā2   | ĪFČĹ   |  |  |  |

| EOI      | 2 3     | EOI                      | EOI    | ĒŌĪ    | EOI    |  |  |  |

| ATN      | 4       | ATN                      | ATN    | ATN    | ATN    |  |  |  |

\*Note: These pins are the IEEE-488 bus non-inverting driver/receivers. They include all the bus terminations required by the Standard and may be connected directly to the GPIB bus connector.

## **GENERAL DESCRIPTION**

The 8293 is a bidirectional transceiver. It was designed to interface the Intel 8291A GPIB Talker/Listener and the Intel® 8292 GPIB Controller to the IEEE Standard 488-1978 Instrumentation Bus (also referred to as the GPIB). The Intel GPIB Transceiver meets or exceeds all of the electrical specifications defined in the IEEE Standard 488-1978, Section 3.3-3.5, including the bus termination specifications.

The 8293 can be hardware programmed to one of four modes of operation. These modes allow the 8293 to be configured to support both a Talker/Listener/Controller environment and a Talker/Listener environment. In addition, the 8293 can be used as a general-purpose, three-state (push-pull) or open-collector bus transceiver with nine receiver/drivers. Two modes each are used to support a Talker/Listener (see Figure 3) and a Talker/Listener/Controller environment (see Figure 4). Mode 1 is used in general-purpose environments.

Figure 3. Talker/Listener Configuration

Figure 4. Talker/Listener/Controller Configuration

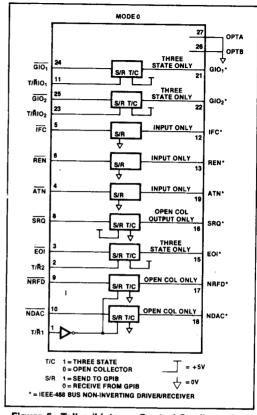

Figure 5. Talker/Listener Control Configuration

Table 3. Mode 0 Pin Description

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                      |

|--------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T/RT1  | 1          | I    | Transmit Receive 1 Direction control for NDAC and NRFD. If T/R1 is high, then NDAC* and NRFD* are receiving. Input is TTL compatible.                                                                  |

| NDAC   | 10         | 1/0  | Not Data Accepted: Processor GPIB bus handshake control line; used to indicate the condition of acceptance of data by device(s). It is TTL compatible.                                                 |

| NDAC*  | 18         | 1/0  | Not Data Accepted: IEEE GPIB bus<br>handshake control line. When an input,<br>it a TTL compatible Schmitt-trigger.<br>When an output, it is an open-collector<br>driver with 48 mA sinking capability. |

| NRFD   | 9          | 1/0  | Not Ready For Data: Processor GPIB handshake control line; used to indicate the condition of readiness of device(s) to accept data. This pin is TTL compatible.                                        |

Table 3. Mode 0 Pin Description (Continued)

| Symbol        | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                      |  |  |

|---------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NRFD*         | 17         | 1/0  | Not Ready For Data: IEEE GPIB bus<br>handshake control line. When an input,<br>it is a TTL compatible Schmitt-trigger.<br>When an output, it is an open-collector<br>driver with a 48 mA current sinking<br>capability.                |  |  |

| T/ <b>R</b> 2 | 2          | 1    | <b>Transmit Receive 2:</b> Direction control for EOI. If T/R2 is high, EOI* is sending. Input is TTL compatible.                                                                                                                       |  |  |

| EOI           | 3          | 1/0  | End Or Identify: Processor GPIB bus control line; is used by a talker to indicate the end of a multiple byte transfer. This pin is TTL compatible.                                                                                     |  |  |

| EOI*          | 15         | 1/0  | End Or Identify: IEEE GPIB bus control line; is used by a talker to indicate the end of a multiple byte transfer. This pin is a three-state (push-pull) driver capable of sinking 48 mA and a TTL compatible receiver with hysteresis. |  |  |

| SRQ           | 8          | ı    | Service Request: Processor GPIB bus control line; used by a device to indicate the need for service and to request an interruption of the current sequence of events on the GPIB. It is a TTL compatible input.                        |  |  |

| SRQ*          | 16         | 0    | Service Request: IEEE GPIB bus control line; it is an open collector driver capable of sinking 48 mA.                                                                                                                                  |  |  |

| REN           | 6          | 0    | Remote Enable: Processor GPIB bus control line; used by a controller (in conjunction with other messages) to select between two alternate sources of device programming data (remote or local control). This output is TTL compatible. |  |  |

| REN*          | 13         | 1    | Remote Enable: IEEE GPIB bus control<br>line. This input is a TTL compatible<br>Schmitt-trigger.                                                                                                                                       |  |  |

| ATN           | 4          | 0    | Attention: Processor GPIB bus control line; used by the 8291 to determine how data on the DIO signal lines are to be interpreted. This is a TTL compatible output.                                                                     |  |  |

| ATN*          | 19         |      | Attention: IEEE GPIB bus control line; this input is a TTL compatible Schmitt-trigger.                                                                                                                                                 |  |  |

| ĪFC           | 5          | 0    | Interface Clear: Processor GPIB bus control line; used by a controller to place the interface system into a known quiescent state. It is a TTL compatible output.                                                                      |  |  |

| Symbol           | Pin<br>No. | Туре | Name and Function                                                                                                                |

|------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------|

| IFC*             | 12         | _    | Interface Clear: IEEE GPIB bus control line. This input is a TTL compatible Schmitt-trigger.                                     |

| T/RIO1<br>T/RIO2 | 11<br>23   | 1    | Transmit Receive General IO: Direction control for the two spare transceivers. These pins are TTL compatible.                    |

| GIO1<br>GIO2     | 24<br>25   | 1/0  | <b>General IO:</b> This is the TTL side of the two spare transceivers. These pins are TTL compatible.                            |

| GIO1*<br>GIO2*   | 21<br>22   | 1/0  | <b>General IO:</b> These are spare three-<br>state (push-pull) drivers/Schmitt-trigger<br>receivers. The drivers can sink 48 mA. |

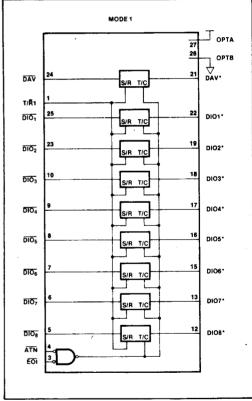

Figure 6. Talker/Listener Data Configuration

Table 4. Mode 1 Pin Description

| Symbo           | Pin<br>No.                              | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T/ <b>R</b> 1   | T/RT 1                                  |      | Transmit Receive 1: Controls the direction for DAV and the DIO lines. If T/R1 is high, then all these lines are sending information to the IEEE GPIB lines. This input is TTL compatible.                                                                                                                                                                                           |

| EOI<br>ATN      | 3 4                                     | 1    | End Of Sequence And Attention: Processor GPIB control lines. These two control signals are ANDed to- gether to determine whether all the transceivers in the 8293 are three- state (push-pull) or open-collector. When both signals are low (true), then the controller is performing a parallel poll and the transceivers are all open-collector. These inputs are TTL compatible. |

| DAV             | 24                                      | 1/0  | Data Valid: Processor GPIB bus<br>handshake control line; used to indi-<br>cate the condition (availability and<br>validity) of information on the DIO<br>lines. It is TTL compatible.                                                                                                                                                                                              |

| DAV*            | 21                                      | 1/0  | Data Valid: IEEE GPIB bus hand-<br>shake control line. When an input, it<br>is a TTL compatible Schmitt-trigger.<br>When DAV* is an output, it can sink 48<br>mA.                                                                                                                                                                                                                   |

| DIO1-<br>DIO8   | 25, 23,<br>10, 9,<br>8, 7,<br>6, 5      | 1/0  | Data Input/Output: Processor GPIB bus data lines; used to carry message and data bytes in a bit-parallel byte-serial form controlled by the three handshake signals. These lines are TTL compatible.                                                                                                                                                                                |

| DIO1*-<br>DIO8* | 22, 19,<br>18, 17,<br>16, 15,<br>13, 12 |      | Data Input/Output: IEEE GPIB bus data lines. They are TTL compatible Schmitt-triggers when used for input and can sink 48 mA when used for output. See ATN and EOI description for output mode.                                                                                                                                                                                     |

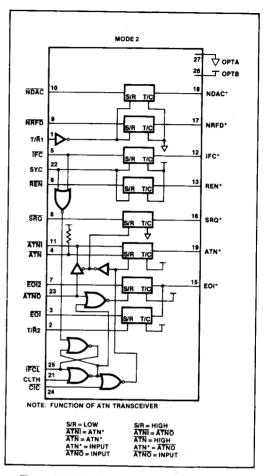

Figure 7. Talker/Listener/Controller Control Configuration

Table 5. Mode 2 Pin Description

| Symbol           | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                        |  |  |  |

|------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| T/Ã1             | 1          | ı    | Transmit Receive 1: Direction control for NDAC and NRFD. If T/R1 is high, then NDAC and NRFD are receiving. Input is TTL compatible.                                                                                                     |  |  |  |

| NDAC             | 10         | I/O  | Not Data Accepted: Processor GPI6 bus handshake control line; used to indicate the condition of acceptance odata by device(s). This pin is TTL compatible.                                                                               |  |  |  |

| NDAC*            | 18         | I/O  | Not Data Accepted: IEEE GPIB bus<br>handshake control line. It is a TTL com-<br>patible Schmitt-trigger when used for<br>input and an open-collector driver with a<br>48 mA current sink capability when used<br>for output.             |  |  |  |

| NRFD             | 9          | I/O  | Not Ready For Data: Processor GPIB bus handshake control line; used to indicate the condition of readiness of device(s) to accept data. This pin is TTL compatible.                                                                      |  |  |  |

| NRFD*            | 17         | I/O  | Not Ready For Data: IEEE GPIB but handshake control line. It is a TTL compatible Schmitt-trigger when used for input and an open-collector driver with a 48 mA current sink capability when used for output.                             |  |  |  |

| syc <sup>1</sup> | 22         | 1    | System Controller: Used to monitor the system controller switch and control the direction for IFC and REN. This pin is a TTL compatible input.                                                                                           |  |  |  |

| REN              | 6          | 1/0  | Remote Enable: Processor GPIB control line; used by the active controller (in conjunction with other messages) to select between two alternate sources of device programming data (remote or local control). This pin is TTL compatible. |  |  |  |

| REN*             | 13         | 1/0  | Remote Enable: IEEE GPIB bus control line. When used as an input, this is a TTL compatible Schmitt-trigger. When an output, it is a three-state driver with a 48 mA current sinking capability.                                          |  |  |  |

| ĪĒČ              | 5          | 1/0  | Interface Clear: Processor GPIB bus control line; used by the active controller to place the interface system into a known quiescent state. This pin is TTL compatible.                                                                  |  |  |  |

| IFC*             | 12         | I/O  | Interface Clear: IEEE GPIB control<br>line. This is a TTL compatible Schmitt-<br>trigger when used for input and a three-<br>state driver capable of sinking 48 mA<br>current when used for output.                                      |  |  |  |

| CIC              | 24         | ı    | Controller In Charge: Used to control the direction of the SRQ and to indicate that the 8292 is in charge of the bus. CIC is a TTL compatible input.                                                                                     |  |  |  |

| Symbol            | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLTH <sup>1</sup> | 21         | ı    | Clear Latch: Used to clear the IFC Received latch after it has been recognize by the 8292. Normally low (except after hardware reset). It will be pulsed hig when IFC Received is recognized by the 8292. This input is TTL compatible.                                                                               |  |  |  |

| ĪFCL.             | 25         | 0    | IFC Received Latch: The 8292 monitors the IFC line when it is not the active controller through this pin.                                                                                                                                                                                                             |  |  |  |

| SRQ               | 8          | 1/0  | Service Request: Processor GPIB control line; indicates the need for attention and requests the active controller to interrupt the current sequence of events on the GPIB bus. This pin is TTL compatible.                                                                                                            |  |  |  |

| SRQ*              | 16         | 1/0  | Service Request: IEEE GPIB bus control line. When used as an input, this pin is a TTL compatible Schmitt-trigger. When used as an output, it is an open-collector driver with a 48 mA current sinking capability.                                                                                                     |  |  |  |

| T/R2              | 2          | 1    | <b>Transmit Receive 2:</b> Controls the direction for EOI. This input is TTL compatible.                                                                                                                                                                                                                              |  |  |  |

| ĀTNO              | 23         | 1    | Attention Out: Processor GPIB bus control line; used by the 8292 for ATN control of the IEEE bus during "take control synchronously" operations. A low on this input causes ATN to be asserted if CIC indicates that this 8292 is in charge. ATNO is a TTL compatible input.                                          |  |  |  |

| ĀTNĪ              | 11         | 0    | Attention In: Processor GPIB bus control line; used by the 8292 to monitor the ATN line. This output is TTL compatible.                                                                                                                                                                                               |  |  |  |

| ATN               | 4          | 0    | Attention: Processor GPIB bus control line; used by the 8292 to monitor the ATN line. This output is TTL compatible.                                                                                                                                                                                                  |  |  |  |

| ATN*              | 19         | 1/0  | Attention: IEEE GPIB bus control line; used by a controller to specify how data on the DIO signal lines are to be interpreted and which devices must respond to data. When used as an output, this pin is a three-state driver capable of sinking 48 mA current. As an input, it is a TTL compatible Schmitt-trigger. |  |  |  |

| EOI2              | 7          | I/O  | End Or Identify 2: Processor GPIB bus<br>control line; used in conjunction with<br>ATN by the active controller (the 8292) to<br>execute a polling sequence. This pin is<br>TTL compatible.                                                                                                                           |  |  |  |

| EOI               | 3          | I/O  | End Or Identify: Processor GPIB bus control line; used by a talker to indicate the end of a multiple byte transfer sequence. This pin is TTL compatible.                                                                                                                                                              |  |  |  |

## NOTES:

V<sub>IL3</sub> is guaranteed at 1.1V on these inputs to accommodate the high current-sourcing capability of these pins during a low input in Mode 2.

Table 5. Mode 2 Pin Description (Continued)

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                          |

|--------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOI*   | 15         | I/O  | End Or Identify: IEEE GPIB bus control line; used by a talker to indicate the end of a multiple byte transfer sequence or, by a controller in conjunction with ATN, to execute a polling sequence. When an output, this pin can sink 48 mA current. When an input, it is a TTL compatible Schmitt-trigger. |

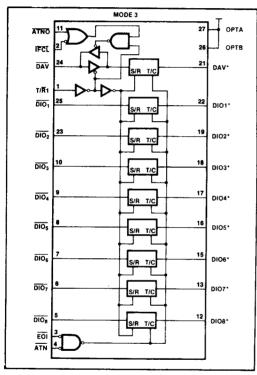

Figure 8. Talker/Listener/Controller Data Configuration

Table 6. Mode 3 Pin Description

| Symbo          | Pin<br>I No.                            | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                               |

|----------------|-----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T/R1           | T/Ř1 1                                  |      | Transmit Receive 1: Controls the direction for DAV and the DIO lines. If T/R1 is high, then all these lines are sending information to the IEEE GPIB lines. This input is TTL compatible.                                                                                                                                                                       |

| ATN            |                                         |      | End Of Sequence and Attention: Processor GPIB control lines. These two control lines are ANDed together to determine whether all the transceivers in the 8293 are push-pull or open-collector. When both signals are low (true), then the controller is performing a parallel poil and the transceivers are all open-collector These inputs are TTL compatible. |

| ATNO           | 11                                      | I    | Attention Out: Processor GPIB control line; used by the 8292 during "take control synchronolisty" operations. This pin is TTL compatible.                                                                                                                                                                                                                       |

| IFCL           | 2                                       | l    | Interface Clear Latched: Used to make DAV received after the system controller asserts IFC. This input is TTL compatible.                                                                                                                                                                                                                                       |

| DAV            | 24                                      | I/O  | Data Valid: Processor GPIB hand-<br>shake control line; used to indicate<br>the condition (availability and<br>validity) of information on the DIO<br>signals. This pin is TTL compatible.                                                                                                                                                                      |

| DAV*           | 21                                      | 1/0  | Data Valid: IEEE GPIB handshake control line. When an input, this pin is a TTL compatible. Schmitt-rrigger, When DAV* is an output, it can sink 48 mA.                                                                                                                                                                                                          |

| DIO1-<br>DIO8  | 25, 23,<br>10, 9,<br>8, 7,<br>6, 5      | I/O  | Data Input/Output: Processor GPIB bus data lines; used to carry message and data bytes in a bit-parallel cyteserial from controlled by the three handshake signals. Those thes are TTL compatible.                                                                                                                                                              |

| DIO1*<br>DIO8* | 22, 19,<br>18, 17,<br>16, 15,<br>13, 12 | 1/0, | Data Input/Output: IEEE GPIS ous data lines They are TTL compatible Schmitt-triggers when used for input and can sink 48 mA when used for output.                                                                                                                                                                                                               |

Figure 9. 8291A and 8293 System Configuration

Figure 10. 8291A, 8292, and 8293 System Configuration

### **ABSOLUTE MAXIMUM RATINGS\***

#### \*NOTICE:

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. All devices are guaranteed to operate within the minimum and maximum parameter limits specified below. Typical parameters however are not tested and are not guaranteed. Established statistically, they indicate the performance level expected in a typical device at room temperature ( $T_A = 25^{\circ}\text{C}$ ) and  $V_{CC} = 5V$ .

## **D.C. CHARACTERISTICS** ( $T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C}, V_{CC} = 5.0\text{V} \pm 10\%, \text{GND} = 0\text{V}$ )

|                    |                                      |        | Limits    |                 | Units | To at Conditions                         |  |

|--------------------|--------------------------------------|--------|-----------|-----------------|-------|------------------------------------------|--|

| Symbol             | Parameter                            | Min.   | Тур.      | Max.            | Units | Test Conditions                          |  |

| V <sub>IL1</sub>   | Input Low Voltage (GPIB Bus Pins)    |        |           | 0.8             | ٧     |                                          |  |

| V <sub>IL2</sub>   | Input Low Voltage (Option Pins)      | -0.1   |           | 0.1             | >     |                                          |  |

| V <sub>IL3</sub> 1 | Input Low Voltage (All Others)       |        |           | 0.8             | ٧     |                                          |  |

| V <sub>IH1</sub>   | Input High Voltage (GPIB Bus Pins)   | 2.0    |           | ν <sub>CC</sub> | ٧     |                                          |  |

| V <sub>IH2</sub>   | Input High Voltage (Option Pins)     | 4.5    |           | ν <sub>cc</sub> | ٧     |                                          |  |

| V <sub>1H3</sub>   | Input High voltage (All Others)      | 2.0    |           | Vcc             | V     |                                          |  |

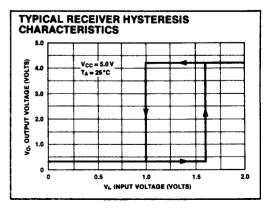

| V <sub>IH4</sub>   | Receiver Input Hysteresis            | 400    |           |                 | mV    |                                          |  |

| V <sub>OL1</sub>   | Output Low Voltage (GPIB Bus Pins)   |        |           | 0.5             | ٧     | I <sub>OL</sub> = 48 mA                  |  |

| V <sub>OL2</sub>   | Output Low Voltage (All Others)      |        |           | 0.5             | >     | I <sub>OL</sub> = 16 mA                  |  |

| V <sub>OH1</sub>   | Output High Voltage (GPIB Bus Pins)  | 2.4    |           | ,               | >     | $I_{OH} = -5.2 \text{ mA}$               |  |

| V <sub>OH2</sub>   | Output High Voltage (All Others)     | 2.4    |           |                 | ٧     | $I_{OH} = -800 \mu A$                    |  |

| V <sub>IT</sub>    | Receiver Input Threshold Low to High | 0.8    |           | 2.0             | >     |                                          |  |

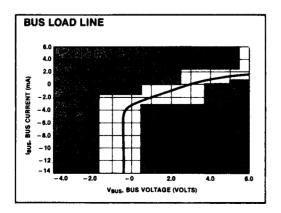

| <sup>I</sup> LC    | Input Load Current (GPIB Pins)       | See Bu | ıs Load l | ine Diag        | am    | $V_{CC} = 5.0V \pm 5\%$                  |  |

| I <sub>I</sub> L   | Input Leakage Current (All Others)   |        |           | 10              | μΑ    | 0.45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |  |

| I <sub>PD</sub>    | Bus Power Down Leakage Current       |        |           | 40              | μΑ    | 0.45V ≤ V <sub>BUS</sub> ≤ 2.7V          |  |

| Icc                | Power Supply Current                 |        | 110       | 175             | mA    |                                          |  |

#### NOTES

### CAPACITANCE

| Symbol           | Parameter                      | Min. | Тур. | Max. | Units | Test Conditions                   |

|------------------|--------------------------------|------|------|------|-------|-----------------------------------|

| C <sub>IO1</sub> | I/O Capacitance (GPIB Side)    |      | 50   | 80   | pF    | V <sub>IN</sub> = V <sub>CC</sub> |

| C <sub>1O2</sub> | I/O Capacitance (System Side)  |      | 35   | 50   | pF    | V <sub>IN</sub> = V <sub>CC</sub> |

| CITR             | Input Capacitance (T/R1, T/R2) |      | 7    | 10   | pF    | V <sub>IN</sub> = V <sub>CC</sub> |

<sup>1.</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

<sup>1.</sup>  $V_{1L3} = 1.1V$  max on pins 21 and 22 in Mode 2 for the 8293-10.

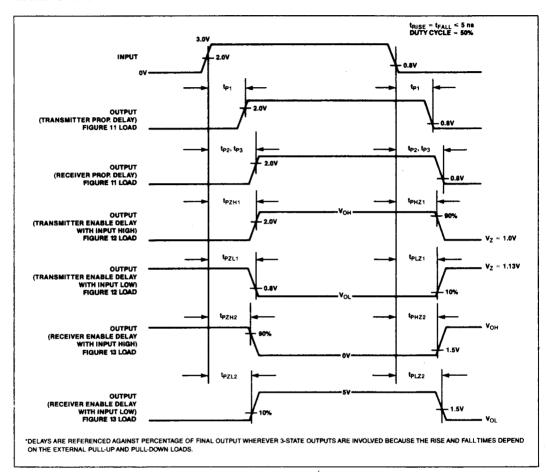

## A.C. CHARACTERISTICS ( $T_A$ = 0°C to 70°C, $V_{CC}$ = 5.0V $\pm$ 10%, GND = 0V)

| Symbol            | Parameter                                                 | Max. | Units<br>ns |

|-------------------|-----------------------------------------------------------|------|-------------|

| t <sub>P1</sub>   | Transmitter Propagation Delay (All Lines)                 | 30   |             |

| t <sub>P2</sub>   | Receiver Propagation Delay (EOI, ATN and Handshake Lines) | 50   | ns          |

| t <sub>P3</sub>   | Receiver Propagation Delay (All Other Lines)              | 60   | ns          |

| t <sub>PHZ1</sub> | Transmitter Disable Delay (High to 3-State)               | 40   | ns          |

| t <sub>PZH1</sub> | Transmitter Enable Delay (3-state to High)                | 40   | ns          |

| t <sub>PLZ1</sub> | Transmitter Disable Delay (Low to 3-State)                | 40   | ns          |

| t <sub>PZL1</sub> | Transmitter Enable Delay (3-State to Low)                 | 40   | ns          |

| t <sub>PHZ2</sub> | Receiver Disable Delay (High to 3-State)                  | 40   | ns          |

| tPZH2             | Receiver Enable Delay (3-State to High)                   | 40   | ns          |

| t <sub>PLZ2</sub> | Receiver Disable Delay (Low to 3-State)                   | 40   | ns          |

| tPZL2             | Receiver Enable Delay (3-State to Low)                    | 40   | ns          |

| tMS               | Mode Switch Delay                                         | 10   | μs          |

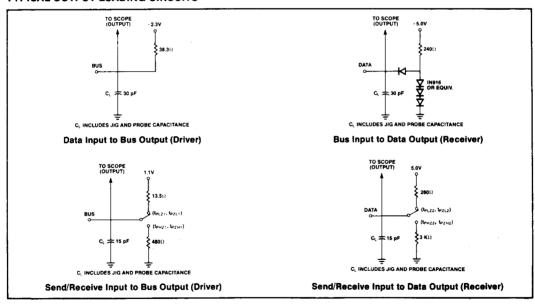

## TYPICAL OUTPUT LOADING CIRCUITS

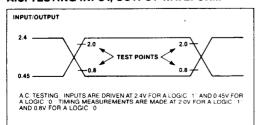

## A.C. TESTING INPUT, OUTPUT WAVEFORM

## **WAVEFORMS**