# 8294 DATA ENCRYPTION UNIT

- Certified by National Bureau of Standards

- 80 Byte/Sec Data Conversion Rate

- 64-Bit Data Encryption Using 56-Bit Key

- DMA Interface

- 3 Interrupt Outputs to Aid in Loading and Unloading Data

- 7-Bit User Output Port

- Single 5V ± 10% Power Supply

- Peripheral to MCS-86<sup>TM</sup>, MCS-85<sup>TM</sup>, MCS-80<sup>TM</sup> and MCS-48<sup>TM</sup> Processors

- Implements Federal Information

Processing Data Encryption Standard

- Encrypt and Decrypt Modes Available

The Intel® 8294 Data Encryption Unit (DEU) is a microprocessor peripheral device designed to encrypt and decrypt 64-bit blocks of data using the algorithm specified in the Federal Information Processing Data Encryption Standard. The DEU operates on 64-bit text words using a 56-bit user-specified key to produce 64-bit cipher words. The operation is reversible: if the cipher word is operated upon, the original text word is produced. The algorithm itself is permanently contained in the 8294; however, the 56-bit key is user-defined and may be changed at any time.

The 56-bit key and 64-bit message data are transferred to and from the 8294 in 8-bit bytes by way of the system data bus. A DMA interface and three interrupt outputs are available to minimize software overhead associated with data transfer. Also, by using the DMA interface two or more DEUs may be operated in parallel to achieve effective system conversion rates which are virtually any multiple of 80 bytes/second. The 8294 also has a 7-bit TTL compatible output port for user-specified functions.

Because the 8294 implements the NBS encryption algorithm it can be used in a variety of Electronic Funds Transfer applications as well as other electronic banking and data handling applications where data must be encrypted.

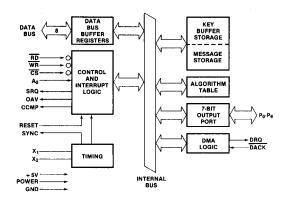

Figure 1. Block Diagram

Figure 2. Pin Configuration

Table 1. Pin Description

|                                                                                                                         | Pin                                          | _        |                                                                                                                      |  |  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                                                                                                                  | No.                                          | Туре     | Name and Function                                                                                                    |  |  |

| NC                                                                                                                      | 1                                            | <u> </u> | No Connection.                                                                                                       |  |  |

| X1<br>X2                                                                                                                | 3                                            | I        | <b>Crystal:</b> Inputs for crystal, L-C or external timing signal to determine internal oscillator frequency.        |  |  |

| RESET                                                                                                                   | 4                                            | 1        | Reset: A low signal to this pin resets the 8294.                                                                     |  |  |

| NC                                                                                                                      | 5                                            |          | No Connection: No connection or tied high.                                                                           |  |  |

| CS                                                                                                                      | 6                                            | 1        | Chip Select: A low signal to this pin enables reading and writing to the 8294.                                       |  |  |

| GND                                                                                                                     | 7                                            |          | <b>Ground:</b> This pin must be tied to ground.                                                                      |  |  |

| RD                                                                                                                      | 8                                            | 1        | Read: An active low read strobe at this pin enables the CPU to read data and status from the internal DEU registers. |  |  |

| A <sub>0</sub>                                                                                                          | 9                                            | ı        | Address: Address input used by the CPU to select DEU registers during read and write operations.                     |  |  |

| WR                                                                                                                      | 10                                           | I        | Write: An active low write strobe at this pin enables the CPU to send data and commands to the DEU.                  |  |  |

| SYNC                                                                                                                    | 11                                           | 0        | Sync: High frequency (Clock ÷ 15) output. Can be used as a strobe for external circuitry.                            |  |  |

| D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | I/O      | <b>Data Bus:</b> Three-state, bi-directional data bus lines used to transfer data between the CPU and the 8294.      |  |  |

| GND                                                                                                                     | 20                                           |          | <b>Ground:</b> This pin must be tied to ground.                                                                      |  |  |

| V <sub>cc</sub>                                                                                                         | 40                                           |          | <b>Power:</b> +5 volt power input: +5V $\pm$ 10%.                                                                    |  |  |

|                                        | Pin                                    |      |                                                                                                                                                                                                                                      |  |  |  |

|----------------------------------------|----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                 | No.                                    | Туре | Name and Function                                                                                                                                                                                                                    |  |  |  |

| NC                                     | 39                                     |      | No Connection.                                                                                                                                                                                                                       |  |  |  |

| DACK                                   | 38                                     | 1    | <b>DMA Acknowledge:</b> Input signal from<br>the 8257 DMA Controller acknowledg-<br>ing that the requested DMA cycle has<br>been granted.                                                                                            |  |  |  |

| DRQ                                    | 37                                     | 0    | <b>DMA Request:</b> Output signal to the 8257 DMA Controller requesting a DMA cycle.                                                                                                                                                 |  |  |  |

| SRQ                                    | 38                                     | 0    | Service Request: Interrupt to the CPU indicating that the 8294 is awaiting data or commands at the input buffer. SRQ=1 implies IBF=0.                                                                                                |  |  |  |

| OAV                                    | 35                                     | 0    | Output Available: Interrupt to the CPI indicating that the 8294 has data of status available in its output buffer OAV=1 implies OBF=1.                                                                                               |  |  |  |

| NC                                     | 34                                     |      | No Connection.                                                                                                                                                                                                                       |  |  |  |

| P6<br>P5<br>P4<br>P3<br>P2<br>P1<br>P0 | 33<br>32<br>31<br>30<br>29<br>28<br>27 | 0    | Output Port: User output port lines. Output lines available to the user via a CPU command which can assert selected port lines. These lines have nothing to do with the encryption function. At power-on, each line is in a 1 state. |  |  |  |

| V <sub>DD</sub>                        | 26                                     |      | Power: +5V power input. (+5V ±10%)<br>Low power standby pin.                                                                                                                                                                         |  |  |  |

| V <sub>cc</sub>                        | 25                                     |      | Power: Tied high.                                                                                                                                                                                                                    |  |  |  |

| CCMP                                   | 24                                     | 0    | Conversion Complete: Interrupt to the CPU indicating that the encryption/decryption of an 8-byte block is complete.                                                                                                                  |  |  |  |

| NC                                     | 23                                     |      | No Connection.                                                                                                                                                                                                                       |  |  |  |

| NC                                     | 22                                     |      | No Connection.                                                                                                                                                                                                                       |  |  |  |

| NC                                     | 21                                     |      | No Connection.                                                                                                                                                                                                                       |  |  |  |

## FUNCTIONAL DESCRIPTION OPERATION

The data conversion sequence is as follows:

- A Set Mode command is given, enabling the desired interrupt outputs.

- An Enter New Key command is issued, followed by 8 data inputs which are retained by the DEU for encryption/decryption. Each byte must have odd parity.

- An Encrypt Data or Decrypt Data command sets the DEU in the desired mode.

After this, data conversions are made by writing 8 data bytes and then reading back 8 converted data bytes. Any of the above commands may be issued between data conversions to change the basic operation of the DEU; e.g., a Decrypt Data command could be issued to change the DEU from encrypt mode to decrypt mode without changing either the key or the interrupt outputs enabled.

#### INTERNAL DEU REGISTERS

Four internal registers are addressable by the master processor: 2 for input, and 2 for output. The following table describes how these registers are accessed.

| RD | WR  | CS | A <sub>0</sub> | Register             |

|----|-----|----|----------------|----------------------|

| 1  | 0   | 0  | 0              | Data input buffer    |

| 0  | 1 . | 0  | 0              | Data output buffer   |

| 1  | 0   | 0  | 1              | Command input buffer |

| 0  | 1   | 0  | 1              | Status output buffer |

| Х  | X   | 1  | Χ              | Don't care           |

The functions of each of these registers are described below.

**Data Input Buffer** — Data written to this register is interpreted in one of three ways, depending on the preceding command sequence.

- 1. Part of a key.

- 2. Data to be encrypted or decrypted.

- 3. A DMA block count.

**Data Output Buffer** — Data read from this register is the output of the encryption/decryption operation.

**Command Input Buffer** — Commands to the DEU are written into this register. (See command summary below.)

Status Output Buffer — DEU status is available in this register at all times. It is used by the processor for poll-driven command and data transfer operations.

STATUS BIT:

7

6

5

4

3

2

1

0

FUNCTION:

X

X

X

KPE

CF

DEC

IBF

OBF

OBF Output Buffer Full; OBF = 1 indicates that output from the encryption/decryption function is available in the Data Output Buffer. It is reset when the data is read.

- IBF Input Buffer Full; A write to the Data Input Buffer or to the Command Input Buffer sets IBF = 1. The DEU resets this flag when it has accepted the input byte. Nothing should be written when IBF = 1.

- DEC Decrypt; indicates whether the DEU is in an encrypt or a decrypt mode. DEC = 1 implies the decrypt mode. DEC = 0 implies the encrypt mode.

- CF Completion Flag; This flag may be used to indicate any or all of three events in the data transfer protocol.

- It may be used in lieu of a counter in the processor routine to flag the end of an 8byte transfer.

- 2. It must be used to indicate the validity of the KPE flag.

- It may be used in lieu of the CCMP interrupt to indicate the completion of a DMA operation.

KPE Key Parity Error; After a new key has been entered, the DEU uses this flag in conjunction with the CF flag to indicate correct or incorrect parity.

#### **COMMAND SUMMARY**

#### 1 — Enter New Key

OP CODE: 0 1 0 0 0 0 0 0

This command is followed by 8 data byte inputs which are retained in the key buffer (RAM) to be used in encrypting and decrypting data. These data bytes must have odd parity represented by the LSB.

#### 2 - Encrypt Data

OP CODE: 0 0 1 1 0 0 0 0

This command puts the 8294 into the encrypt mode.

#### 3 - Decrypt Data

OP CODE: 0 0 1 0 0 0 0

This command puts the 8294 into the decrypt mode.

#### 4 - Set Mode

OP CODE:

0 0 0 0 A B C D

MSB LSI

#### where:

A is the OAV (Output Available) interrupt enable B is the SRQ (Service Request) interrupt enable C is the DMA (Direct Memory Access) transfer enable D is the CCMP (Conversion Complete) interrupt enable

This command determines which interrupt outputs will be enabled. A "1" in bits A, B, or D will enable the OAV, SRQ, or CCMP interrupts respectively. A "1" in bit C will allow DMA transfers. When bit C is set the OAV and Following the command in which bit C, the DMA bit, is set, the 8294 will expect one data byte to specify the number of 8-byte blocks to be converted using DMA.

#### 5 - Write to Output Port

OP CODE: 1 P<sub>6</sub> P<sub>5</sub> P<sub>4</sub> P<sub>3</sub> P<sub>2</sub> P<sub>1</sub> P<sub>0</sub>

MSB LSB

This command causes the 7 least significant bits of the command byte to be latched as output data on the 8294 output port. The initial output data is 1111111. Use of this port is independent of the encryption/decryption function.

## PROCESSOR/DEU INTERFACE PROTOCOL ENTERING A NEW KEY

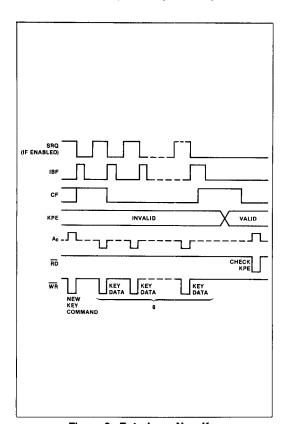

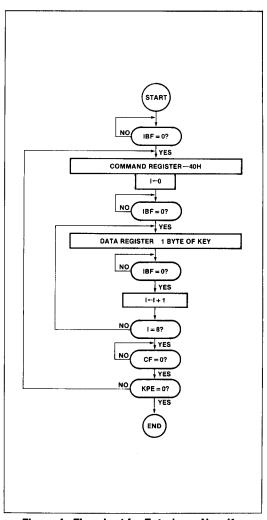

The timing sequence for entering a new key is shown in Figure 3. A flowchart showing the CPU software to accommodate this sequence is given in Figure 4.

Figure 3. Entering a New Key

After the Enter New Key command is issued, 8 data bytes representing the new key are written to the data input buffer (most significant byte first). After the eighth byte is accepted by the DEU, CF goes true (CF = 1). The CF bit goes false again when KPE is valid. The CPU can then check the KPE flag. If KPE = 1, a parity error has been detected and the DEU has not accepted the key. Each byte is checked for odd parity, where the parity bit is the LSB of each byte.

Since the CF bit is used in this protocol to indicate the validity of the KPE flag, it may not be used to flag the end of the 8 byte key entry. CF = 1 only as long as KPE is invalid. Therefore, the CPU might not detect that CF = 1 and the key entry is complete before KPE becomes valid. Thus, a counter should be used, as in Figure 4, to flag the end of the new key entry. Then, CF is used to indicate a valid KPE flag.

Figure 4. Flowchart for Entering a New Key

#### **ENCRYPTING OR DECRYPTING DATA**

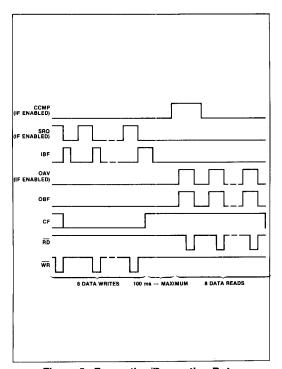

Figure 5 shows the timing sequence for encrypting or decrypting data. The CPU writes 8 data bytes to the DEU's data input buffer for encryption/decryption. CF then goes true (CF = 1) to indicate that the DEU has accepted the 8-byte block. Thus, the CPU may test for IBF = 0 and CF = 1 to terminate the input mode, or it may use a software counter. When the encryption/decryption is complete, the CCMP and OAV interrupts are asserted and the OBF flag is set true (OBF = 1). OAV and OBF are set false again after each of the converted data bytes is read back by the CPU. The CCMP interrupt is set false, and remains false, after the first read. After 8 bytes have been read back by the CPU, CF goes false (CF = 0). Thus, the CPU may test for CF = 0 to terminate the read mode. Also, the CCMP interrupt may be used to initiate a service routine which performs the next series of 8 data reads and 8 data writes.

Figure 5. Encrypting/Decrypting Data

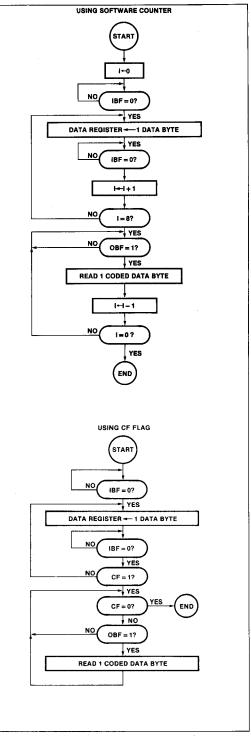

Figure 6 offers two flowcharts outlining the alternative means of implementing the data conversion protocol. Either the CF flag or a software counter may be used to end the read and write modes.

SRQ = 1 implies IBF = 0, OAV = 1 implies OBF = 1. This allows interrupt routines to do data transfers without checking status first. However, the OAV service routine must detect and flag the end of a data conversion.

Figure 6. Data Conversion Flowcharts

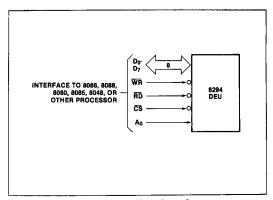

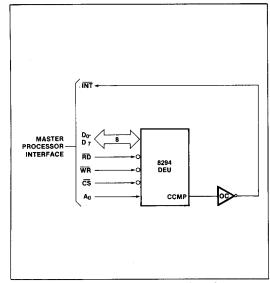

#### **CPUIDEU INTERFACES**

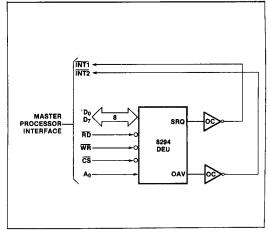

Figures 12 through 15 illustrate four interface configurations used in the CPU/DEU data transfers. In all cases SRQ will be true (if enabled) and IBE will be false when the DEU is ready to accept data or commands.

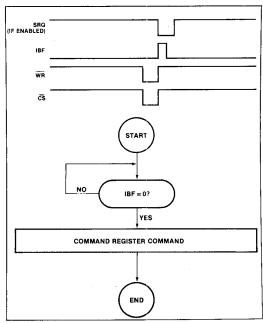

Figure 10. Single Byte Commands

Figure 11. Pacify Protocol

Figure 12. Polling Interface

Figure 13. Single interrupt interface

Figure 14. Dual Interrupt Interface

8-336 AFN-00230C

#### **USING DMA**

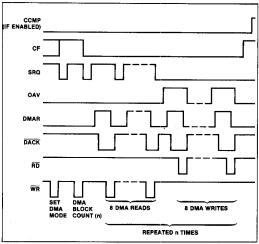

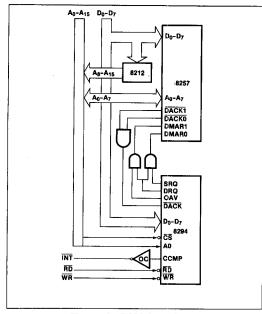

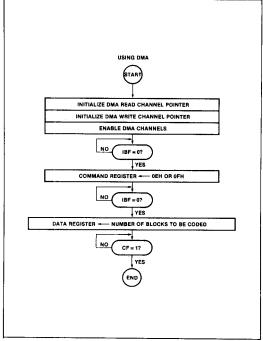

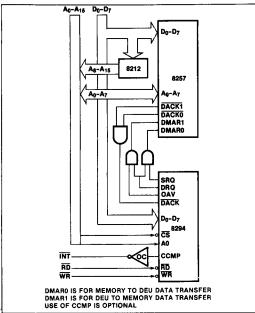

The timing sequence for data conversions using DMA is shown in Figure 7. This sequence can be better understood when considered in conjunction with the hardware DMA interface in Figure 8. Note that the use of the DMA feature requires 3 external AND gates and 2 DMA channels (one for input, one for output). Since the DEU has only one DMA request pin, the SRQ and OAV outputs are used in conjunction with two of the AND gates to create separate DMA request outputs for the 2 DMA channels. The third AND gate combines the two active-low DACK inputs.

Figure 7. DMA Sequence

Figure 8. DMA Interface

To initiate a DMA transfer, the CPU must first initialize the two DMA channels as shown in the flowchart in Figure 9. It must then issue a Set Mode command to the DEU enabling the OAV, SRQ, and DMA outputs. The CCMP interrupt may be enabled or disabled, depending on whether that output is desired. Following the Set Mode command, there must be a data byte giving the number of 8-byte blocks of data (n<256) to be converted. The DEU then generates the required number of DMA requests to the 2 DMA channels with no further CPU intervention. When the requested number of blocks has been converted, the DEU will set CF and assert the CCMP interrupt (if enabled). CCMP then goes false again with the next write to the DEU (command or data). Upon completion of the conversion, the DMA mode is disabled and the DEU returns to the encrypt/decrypt mode. The enabled interrupt outputs, however, will remain enabled until another Set Mode command is issued.

Figure 9. DMA Flowchart

#### SINGLE BYTE COMMANDS

Figure 10 shows the timing and protocol for single byte commands. Note that any of the commands is effective as a pacify command in that they may be entered at any time, except during a DMA conversion. The DEU is thus set to a known state. However, if a command is issued out of sequence, an additional protocol is required (Figure 11). The CPU must wait until the command is accepted (IBF = 0). A data read must then be issued to clear anything the preceding command sequence may have left in the Data Output Buffer.

Figure 18. Recommended Connection for External Clock Signal

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias | 0°C to 70°C        |

|--------------------------------|--------------------|

| Storage Temperature 6          | 65°C to + 150°C    |

| Voltage on Any Pin With        |                    |

| Respect to Ground              | . $-0.5V$ to $+7V$ |

| Power Dissipation              | 1.5 Watt           |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. AND OPERATING CHARACTERISTICS ( $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = +5V \pm 10\%$ , $V_{SS} = 0V$ )

| Symbol                            | Parameter                                                               |           | Limits |                 | Unit    | Test Conditions                                     |

|-----------------------------------|-------------------------------------------------------------------------|-----------|--------|-----------------|---------|-----------------------------------------------------|

|                                   | Faranteter                                                              | Min. Typ. |        | Max.            | 1 01111 | lest Coliditions                                    |

| V <sub>IL</sub>                   | Input Low Voltage (All Except X <sub>1</sub> , X <sub>2</sub> , RESET)  | -0.5      |        | 0.8             | ٧       |                                                     |

| V <sub>IL1</sub>                  | Input Low Voltage (X <sub>1</sub> , X <sub>2</sub> , RESET)             | -0.5      |        | 0.6             | V       |                                                     |

| V <sub>IH</sub>                   | Input High Voltage (All Except X <sub>1</sub> , X <sub>2</sub> , RESET) | 2.2       |        | V <sub>CC</sub> | ٧       |                                                     |

| V <sub>IH1</sub>                  | Input High Voltage (X <sub>1</sub> , X <sub>2</sub> , RESET)            | 3.8       |        | V <sub>cc</sub> | ٧       |                                                     |

| VoL                               | Output Low Voltage (D <sub>0</sub> -D <sub>7</sub> )                    |           |        | 0.45            | V       | I <sub>OL</sub> = 2.0 mA                            |

| V <sub>OL1</sub>                  | Output Low Voltage (All<br>Other Outputs)                               |           |        | 0.45            | ٧       | I <sub>OL</sub> = 1.6 mA                            |

| V <sub>OH</sub>                   | Output High Voltage (D <sub>0</sub> -D <sub>7</sub> )                   | 2.4       |        |                 | V       | $I_{OH} = -400 \mu A$                               |

| V <sub>OH1</sub>                  | Output High Voltage (All<br>Other Outputs)                              | 2.4       |        |                 | ٧       | l <sub>OH</sub> = -50 μA                            |

| l <sub>IL</sub>                   | Input Leakage Current (RD, WR, CS, A <sub>0</sub> )                     |           |        | ±10             | μА      | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |

| loz                               | Output Leakage Current (D <sub>0</sub> -D <sub>7</sub> , High Z State)  |           |        | ±10             | μΑ      | $V_{SS} + 0.45 \le V_{OUT} \le V_{CC}$              |

| I <sub>DD</sub>                   | V <sub>DD</sub> Supply Current                                          |           | 5      | 15              | mA      |                                                     |

| I <sub>DD</sub> + I <sub>CC</sub> | Total Supply Current                                                    | 1         | 60     | 125             | mA      |                                                     |

| lu .                              | Low Input Load Current<br>(Pins 24, 27-38)                              |           |        | 0.5             | mA      | V <sub>IL</sub> = 0.8 V                             |

| I <sub>LI1</sub>                  | Low Input Load Current (RESET)                                          |           |        | 0.2             | mA      | V <sub>IL</sub> = 0.8 V                             |

| liн                               | Input High Leakage Current<br>(Pins 24, 27-38)                          |           |        | 100             | μΑ      | V <sub>IN</sub> = V <sub>CC</sub>                   |

| CIN                               | Input Capacitance                                                       |           |        | 10              | pF      |                                                     |

| C <sub>I/O</sub>                  | I/O Capacitance                                                         |           |        | 20              | pF      |                                                     |

Figure 15. DMA interface

#### **OSCILLATOR AND TIMING CIRCUITS**

The 8294's internal timing generation is controlled by a self-contained oscillator and timing circuit. A choice of crystal, L-C or external clock can be used to derive the basic oscillator frequency.

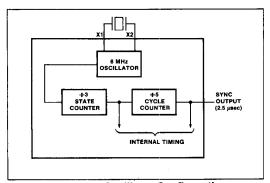

The resident timing circuit consists of an oscillator, a state counter and a cycle counter as illustrated in Figure 16.

Figure 16. Oscillator Configuration

#### **OSCILLATOR**

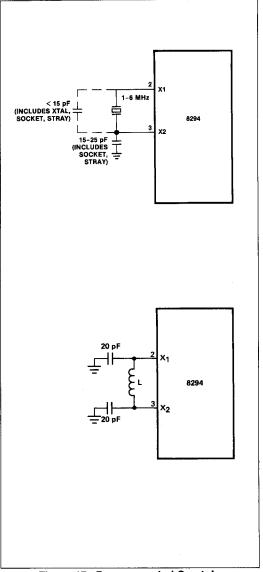

The on-board oscillator is a series resonant circuit with a frequency range of 1 to 6 MHz. Pins X1 and X2 are input and output (respectively) of a high gain amplifier stage. A crystal or inductor and capacitator connected between X1 and X2 provide the feedback and proper phase shift for oscillation. Recommended connections for crystal or L-C are shown in Figure 17.

Figure 17. Recommended Crystal and L-C Connections

A recommended range of inductance and capacitance combinations is given below:

$L = 120 \mu H$  corresponds to 3 MHz

$L = 45 \mu H$  corresponds to 5 MHz

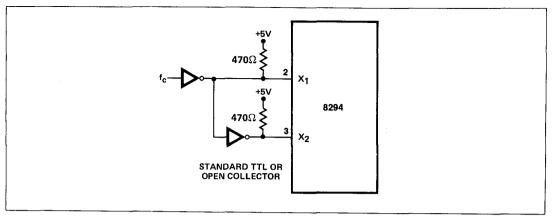

An external clock signal can also be used as a frequency reference to the 8294; however, the levels are *not* compatible. The signal must be in the 1 MHz-6 MHz frequency range and must be connected to pins X1 and X2 by buffers with a suitable pull-up resistor to guarantee that a logic "1" is above 3.8 volts. The recommended connection is shown in Figure 18.

## **WAVEFORMS**

## A.C. CHARACTERISTICS ( $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = V_{DD} = +5V \pm 10\%$ , $V_{SS} = 0V$ )

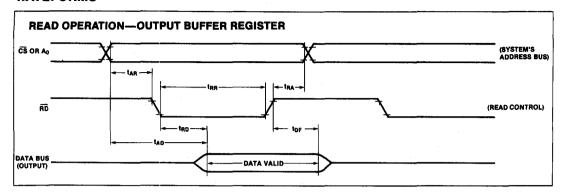

## **DBB READ**

| Symbol          | Parameter                            | Min. | Max. | Unit | Test Conditions         |

|-----------------|--------------------------------------|------|------|------|-------------------------|

| t <sub>AR</sub> | CS, A <sub>0</sub> Setup to RD ↓     | 0    |      | ns   |                         |

| t <sub>RA</sub> | ĈŜ, A₀ Hold After RD ↑               | 0    |      | ns   |                         |

| t <sub>RR</sub> | RD Pulse Width                       | 250  |      | ns   |                         |

| t <sub>AD</sub> | CS, A <sub>0</sub> to Data Out Delay |      | 225  | ns   | C <sub>L</sub> = 150 pF |

| t <sub>RD</sub> | RD ↓ to Data Out Delay               |      | 225  | ns   | C <sub>L</sub> = 150 pF |

| t <sub>DF</sub> | RD ↑ to Data Float Delay             |      | 100  | ns   |                         |

| t <sub>CY</sub> | Cycle Time                           | 2.5  | 15   | μs   | 6 MHz Crystal           |

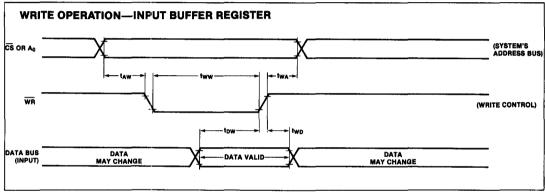

## **DBB WRITE**

| Symbol          | Parameter                          | Min. | Max. | Unit | Test Conditions |

|-----------------|------------------------------------|------|------|------|-----------------|

| t <sub>AW</sub> | CS, A <sub>0</sub> Setup to WR ↓   | 0    |      | ns   |                 |

| twA             | ČŠ, A <sub>0</sub> Hold After WR ↑ | 0    |      | ns   |                 |

| tww             | WR Pulse Width                     | 250  |      | ns   |                 |

| t <sub>DW</sub> | Data Setup to WR ↑                 | 150  |      | ns   |                 |

| twp             | Data Hold to WR ↑                  | 0    |      | ns   |                 |

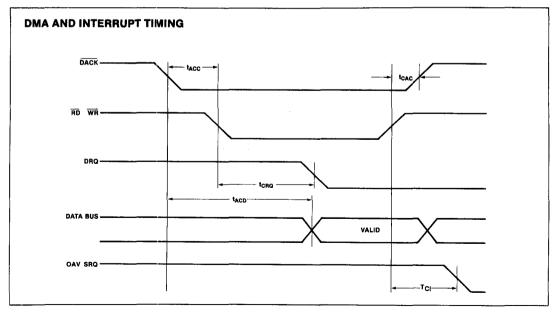

## **DMA AND INTERRUPT TIMING**

| Symbol           | Parameter                      | Min. | Max.                  | Unit | Test Conditions          |

|------------------|--------------------------------|------|-----------------------|------|--------------------------|

| t <sub>ACC</sub> | DACK Setup to Control          | 0    |                       | ns   |                          |

| t <sub>CAC</sub> | DACK Hold After Control        | 0    |                       | ns   |                          |

| t <sub>ACD</sub> | DACK to Data Valid             |      | 225                   | ns   | $C_{L} = 150 \text{ pF}$ |

| t <sub>CRQ</sub> | Control L.E. to DRQ T.E.       |      | 200                   | ns   |                          |

| t <sub>Cl</sub>  | Control T.E. to Interrupt T.E. |      | t <sub>CY</sub> + 500 | ns   |                          |

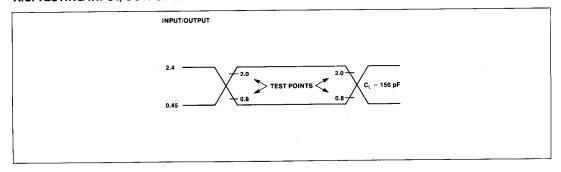

## A.C. TESTING INPUT, OUTPUT WAVEFORM

8-339 AFN-00230C