## 8296/8297 GPIB BUS TRANSCEIVER

- Octal Open-Collector or Three-State GPIB Line Drivers

- Octal Schmitt-Type Line Receivers

- Low-Power HMOS II Design

- Power Up/Power Down Protection to Prevent Disrupting the Bus

- Two 20-Pin Transceivers Connect 8291 Directly to GPIB Bus Including On-Chip IEEE-488 Bus Terminations

- Only 8291, 8296, and 8297 Required to Form Complete IEEE-488 Talker/ Listener Interface with No Additional Components

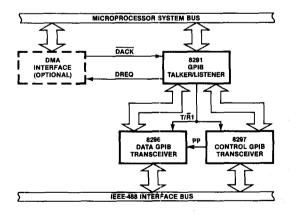

The Intel® 8296/8297 GPIB Bus Transceivers are high-current, non-inverting buffer chips designed to interface the 8291 GPIB Talker/Listener to the IEEE Standard 488-1978 Instrumentation Interface Bus. The 8296 and 8297 are optimized to simplify a talker/listener configuration so that the 8291 can be connected to the GPIB bus without any external hardware. The 8297 connects the five IEEE-488 control lines and three handshake lines to the 8291 with a special output for parallel poll. The 8296 connects the eight data lines to the 8291, or it can be used as a general purpose high-current bus transceiver.

Figure 1. 8291, 8296, 8297 System Diagram

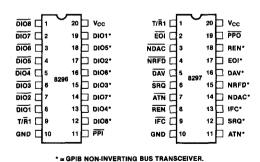

Figure 2. Pin Configuration

Table 2. 8297 Pin Description

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                       |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T/R1   | 1          |      | Transmit/Receive 1: Direction control for NDAC, NRFD, and DAV. EOI' is gated by ATN' and T/R1 so that it will remain an input during a parallel poll. If T/R1 is high, then NDAC' and NRFD' are inputs while DAV' and EOI' (if ATN' is high) are outputs. This input is TTL compatible. |

| ĒŌĪ    | 2          | I/O  | End or Identify: Processor GPIB control line; used by a talker to indicate the end of a multiple byte transfer. This pin is TTL compatible.                                                                                                                                             |

| NDAC   | 3          | 1/0  | Not Data Accepted: Processor<br>GPIB handshake line; used to indi-<br>cate the data has been accepted by<br>all listeners. This pin is TTL com-<br>patible.                                                                                                                             |

| NRFD   | 4          | 1/0  | Not Ready For Data: Processor<br>GPIB handshake line; used to indi-<br>cate the listener is ready to accept<br>another byte. This pin is TTL<br>compatible.                                                                                                                             |

| DAV    | 5          | I/O  | Data Available: Processor GPIB handshake line; used to indicate the talker has inserted data onto the bus. This pin is TTL compatible.                                                                                                                                                  |

| SRQ    | 6          | '    | Service Request: Processor GPIB control line; used to indicate the need for service. This input is TTL compatible.                                                                                                                                                                      |

| ĀTN    | 7          | 0    | Attention: Processor GPIB control line; used to determine whether the byte being received is data or control. This output is TTL compatible.                                                                                                                                            |

| REN    | 8          | 0    | Remote Enable: Processor GPIB control line; used to select between remote or local device programming. This output is TTL compatible.                                                                                                                                                   |

| IFC    | 9          | 0    | Interface Clear: Processor GPIB control line; used to reset the interface. This output is TTL compatible.                                                                                                                                                                               |

| GND    | 10         | PS   | Circuit Ground Potential.                                                                                                                                                                                                                                                               |

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                      |

|--------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | NO.        | Type | Name and Function                                                                                                                                                                                                                                                      |

| Vcc    | 20         | PS   | Positive Power Supply: (5V ±10%).                                                                                                                                                                                                                                      |

| PPO    | 19         | 0    | Parallel Poll Out: Signal to the 8296 to indicate a parallel poll is being performed (both ATN* and EOI* are low).                                                                                                                                                     |

| REN*   | 18         | ı    | Remote Enable: IEEE-488 GPIB control line; this input is an IEEE-488 compatible Schmitt trigger.                                                                                                                                                                       |

| EOI*   | 17         | I/O  | End or Identify: IEEE-488 GPIB control line; used by a talker to indicate the end of a message, and by the controller with ATN* to indicate a parallel poll. It is an input whenever ATN* is low or T/R1 is low. This pin is IEEE-488 compatible for input and output. |

| DAV*   | 16         | I/O  | Data Available: IEEE-488 GPIB handshake line; is a GPIB driver when T/R1 is high and is push-pull except during a parallel poll. This pin is IEEE-488 compatible for input and output.                                                                                 |

| NRFD*  | 15         | 1/0  | Not Ready For Data: IEEE-488 GPIB handshake line; is an open-collector GPIB driver when T/R1 is low. This pin is IEEE-488 compatible for input and output.                                                                                                             |

| NDAC*  | 14         | I/O  | Not Data Accepted: IEEE-488 GPIB handshake line; is an open-collector GPIB driver when T/R1 is low. This pin is IEEE-488 compatible for input and output.                                                                                                              |

| IFC*   | 13         | I    | Interface Clear: IEEE-488 GPIB control line; this input is an IEEE-488 compatible Schmitt trigger.                                                                                                                                                                     |

| SRQ*   | 12         | 0    | Service Request: IEEE-488 GPIB control line; this output is an open-collector IEEE-488 compatible driver.                                                                                                                                                              |

| ATN*   | 11         | 1    | Attention: IEEE-488 GPIB control line; this input is an IEEE-488 compatible Schmitt trigger.                                                                                                                                                                           |

| Table 1. | 8296 | Pin | Descri | ption |

|----------|------|-----|--------|-------|

|----------|------|-----|--------|-------|

| Symbol        | Pin No. | Туре | Name and Function                                                                                                                                                                              |

|---------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIO8-<br>DIO1 | 1-8     | I/O  | Data Input/Output: Processor GPIB data lines; used to carry message and data bytes in a bit-parallel byteserial form. If T/R1 is high, these lines are inputs. These lines are TTL compatible. |

| T/R1          | 9       | ı    | Transmit/Receive 1: Controls the direction of the DiO lines. If T/R1 is high, then the eight DIO lines are driving data onto the IEEE-488 bus. This input is TTL compatible.                   |

| GND           | 10      | PS   | Circuit Ground Potential.                                                                                                                                                                      |

| Symbol          | Pin No.                           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> | 20                                | PS   | Positive Power Supply: (5V ±10%).                                                                                                                                                                                                                                                                                                                                                            |

| DIO1*-<br>DIO8* | 19, 17, 15, 13,<br>18, 16, 14, 12 | 1/0  | Data Input/Output: IEEE-488 GPIB data lines. They are IEEE-488 compatible Schmitt triggers when used for input and can sink over 48 mA when used for output. If T/R1 is high, these lines are driving the bus. If PPI is high, then these lines are open-collector for a parallel poll; otherwise, they are push-pull line drivers. These pins are IEEE-488 compatible for input and output. |

| PPI             | 11                                | I    | Parallel Poll In: Input from<br>the 8297 which indicates<br>whether or not a parallel poll<br>is being conducted. The 8296<br>is a push-pull (three-state)<br>driver for data bytes, but it<br>becomes an open-collector<br>driver for a parallel poll.                                                                                                                                      |

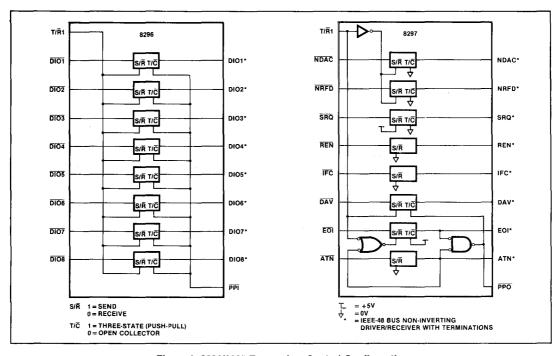

Figure 3. 8296/8297 Transceiver Control Configuration

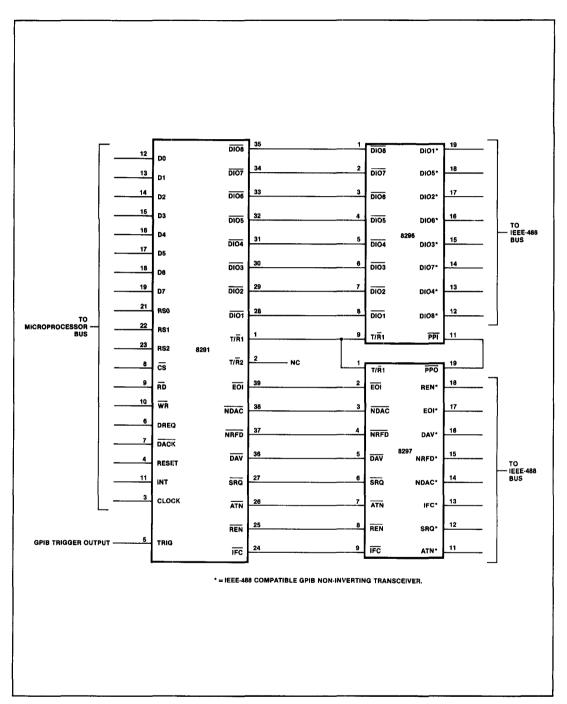

Figure 4. 8291, 8296, 8297 System Configuration