# SPCP02A

## **Keyboard Controller**

AUG. 05, 2003

Version 1.1

SUNPLUS TECHNOLOGY CO. reserves the right to change this documentation without prior notice. Information provided by SUNPLUS TECHNOLOGY CO. is believed to be accurate and reliable. However, SUNPLUS TECHNOLOGY CO. makes no warranty for any errors which may appear in this document. Contact SUNPLUS TECHNOLOGY CO. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by SUNPLUS TECHNOLOGY CO. for any infringement of patent or other rights of third parties which may result from its use. In addition, SUNPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Sunplus.

### SPCP02A

### **Table of Contents**

### **PAGE**

| 1. | GENERAL DESCRIPTION                                             | 3          |

|----|-----------------------------------------------------------------|------------|

| 2. | BLOCK DIAGRAM                                                   | 3          |

| 3. | FEATURES                                                        | 3          |

| 4. | SIGNAL DESCRIPTIONS                                             | 4          |

|    | 4.1. ORDERING INFORMATION                                       | 4          |

|    | 4.2. PIN ASSIGNMENT                                             | <u>,</u> 5 |

| 5. | FUNCTIONAL DESCRIPTIONS                                         |            |

|    | 5.1. CPU                                                        | <u> </u>   |

|    | 5.2. MEMORY                                                     | 6          |

|    | 5.3. Oscillator                                                 | 7          |

|    | 5.4. CONTROL REGISTER SUMMARY                                   | 8          |

|    | 5.5. PORT A GROUP                                               | 9          |

|    | 5.6. PORT B GROUP                                               | 10         |

|    | 5.7. PORT C GROUP                                               | 12         |

|    | 5.8. PORT D GROUP                                               | 14         |

|    | 5.9. PORT E GROUP                                               | 15         |

|    | 5.10. PORT F GROUP                                              | 16         |

|    | 5.11. INTERRUPT                                                 | 17         |

|    | 5.12. TIMER1 & REAL TIME INTERRUPT                              | 19         |

|    | 5.13. STOP Mode                                                 | 21         |

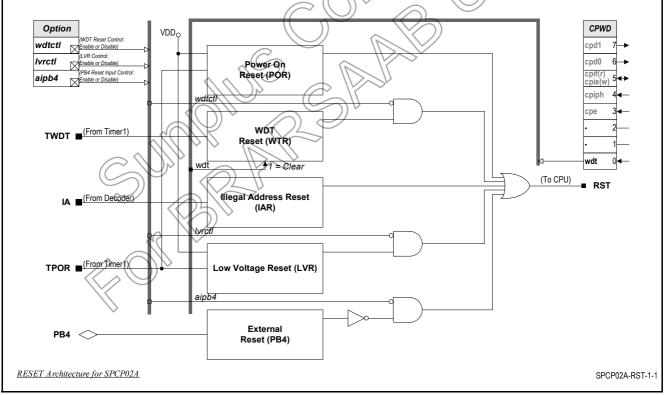

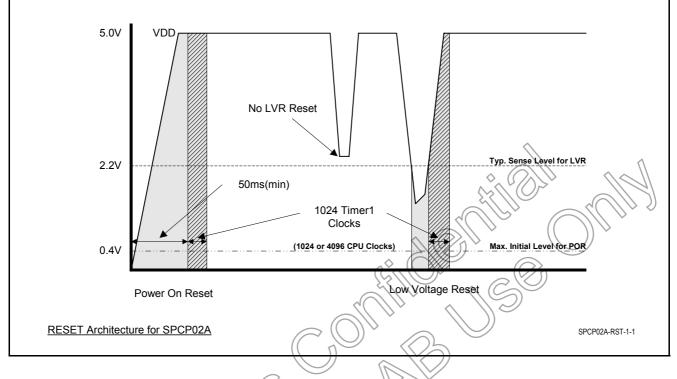

|    | 5.14. RESET                                                     | 21         |

|    | 5.15. SPECIAL SHADOW REGISTER                                   | 23         |

|    | 5.16. MASK OPTIONS                                              | 24         |

| 6. | ELECTRICAL SPECIFICATIONS                                       | 25         |

|    | 6.1. ITEM DEFINITION                                            | 25         |

|    | 6.2. ABSOLUTE MAXIMUM RATING                                    |            |

|    | 6.3. RECOMMENDED OPERATING CONDITIONS                           |            |

|    | 6.4. PIN ATTRIBUTE DESCRIPTION (VDD = 5.0V, TEMPERATURE = 25°C) |            |

|    | 6.5. R-OSC FREQUENCY REFERENCE DATA                             |            |

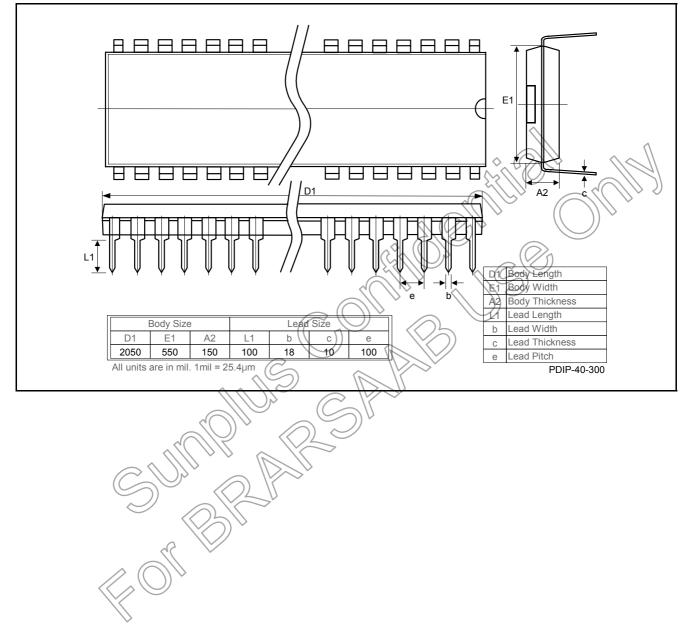

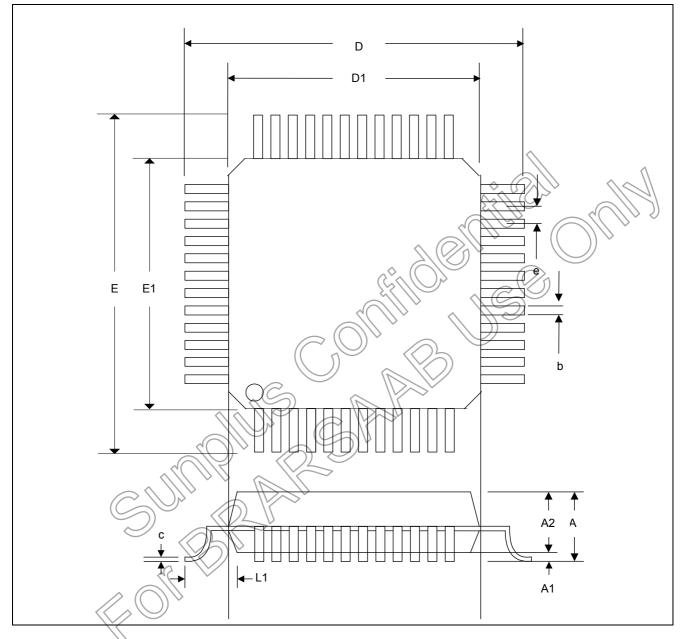

| 7. | PACKAGE/PAD LOCATIONS                                           | 27         |

|    | 7.1. PAD ASSIGNMENT AND LOCATIONS                               |            |

|    | 7.2. PACKAGE INFORMATION                                        | 28         |

| 8. | DISCLAIMER                                                      | 30         |

| 9. | REVISION HISTORY                                                | 31         |

### **KEYBOARD CONTROLLER**

### **1. GENERAL DESCRIPTION**

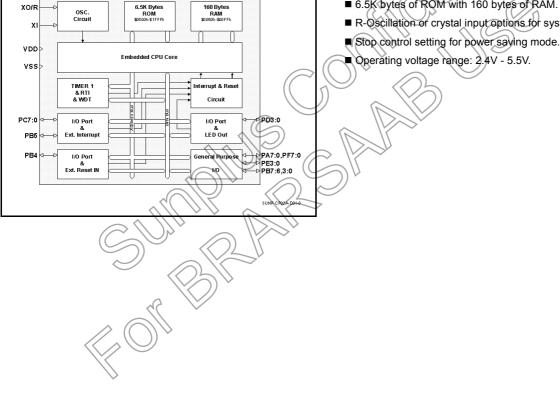

SPCP02A, a 44-pad micro-controller, contains an 8-bit timer, a watchdog timer and 40 general-purpose I/Os that can easily be applied for keyboard applications. Inside the chip, the 8-bit CPU is able to work at the maximum operating frequency of 6MHz. The embedded ROM size is 6.5K bytes, and the embedded SRAM is 160 bytes. In addition, it supports 40/48-pin packages or 44-pad COB solution.

### 2. BLOCK DIAGRAM

XO/F

### **3. FEATURES**

- Built-in 8-bit Sunplus CPU core and up to 6MHz clock operation.

- 40 or 36 general-purpose I/Os that are belong to six groups of I/O ports. Some of them are combined with the options of pull-up/down resistors, or totem pole/open drain outputs

- Four I/O ports can be utilized for LED outputs.

- Two external interrupt groups -- one comes from individual I/O (PB5); the other is a group input, PC port. They can be enabled by mask option

- External reset input option on PB4.

- One 8-bit timer with real time interrupt control.

- A watchdog timer for program control.

- 6.5K bytes of ROM with 160 bytes of RAM.

- R-Oscillation or crystal input options for system clock.

### 4. SIGNAL DESCRIPTIONS

| Mnemonic | 40 PIN<br>PKG | 48 PIN<br>PKG | 44 PAD<br>COB | Description                                                                                                                                                                                                                                                                              |

|----------|---------------|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | 1             | 42            | 1             | System Ground.                                                                                                                                                                                                                                                                           |

| PD3      | 2             | 43            | 2             | <u>GPIO Port D3 Output (LED Output 3)</u> . This I/O channel can be LED high current driven output or general I/O. Use internal setting to configure it.                                                                                                                                 |

| PE0:1    | 3:4           | 44:45         | 3:4           | <u>GPIO Port E0:1</u> . General-purpose input/output or PS/2 interface by programming configuration.                                                                                                                                                                                     |

| PE2:3    |               | 46:47         | 5:6           | <u>GPIO Port E2:3</u> . General-purpose input/outputs or PS/2 interface by programming configuration.                                                                                                                                                                                    |

| PB0:3    | 5:8           | 48,1:3        | 7:10          | GPIO Port B0:3. General-purpose input/outputs by programming configuration.                                                                                                                                                                                                              |

| PB4:5    | 9:10          | 4:5           | 11:12         | <u>GPIO Port B4:5</u> . General-purpose inputs/output by programming configuration. In addition, PB4 can be used as the Main RESET input. PB5 can be used as the external Main IRQ input.                                                                                                |

| PB6:7    |               | 6:7           | 13:14         | GPIO Port B6:7. General-purpose input/outputs by programming configuration.                                                                                                                                                                                                              |

| PA0:7    | 11:18         | 8:15          | 15:22         | GPIO Port A0:7. General-purpose input/outputs by programming configuration.                                                                                                                                                                                                              |

| PF0:7    | 19:26         | 16:23         | 23:30         | GPIO Port F0:7. General-purpose input/outputs by programming configuration.                                                                                                                                                                                                              |

| PC0:7    | 27:34         | 28:35         | 31:38         | <u>GPIO Port C0:7</u> . General-purpose inputs/outputs by programming configuration. In addition, these pins can be used as the external interrupt inputs.                                                                                                                               |

| PD0:2    | 35:37         | 36:38         | 39:41         | GPIO Port D0:2 Output (LED Output 0:2). These I/O channels can be LED high current driven outputs or general I/Os by programming configuration.                                                                                                                                          |

| VDD      | 38            | 39            | 42            | System Power Supply.                                                                                                                                                                                                                                                                     |

| XO/R     | 39            | 40            | 43            | Crystal In or Resistor In Input. An external resistive pull-up connects with internal OSC circuitry for generating the internal clock and the related time base in R-Oscillation mode. It will be connected with external crystal for a crystal oscillation circuitry in crystal mode.   |

| XI       | 40            | 41            | 44            | <u>Crystal Output or External Clock Input</u> . External clock input connects with internal clock circuitry to generate the internal clock and related time base in external clock mode. It will be connected with external crystal for a crystal oscillation circuitry in crystal mode. |

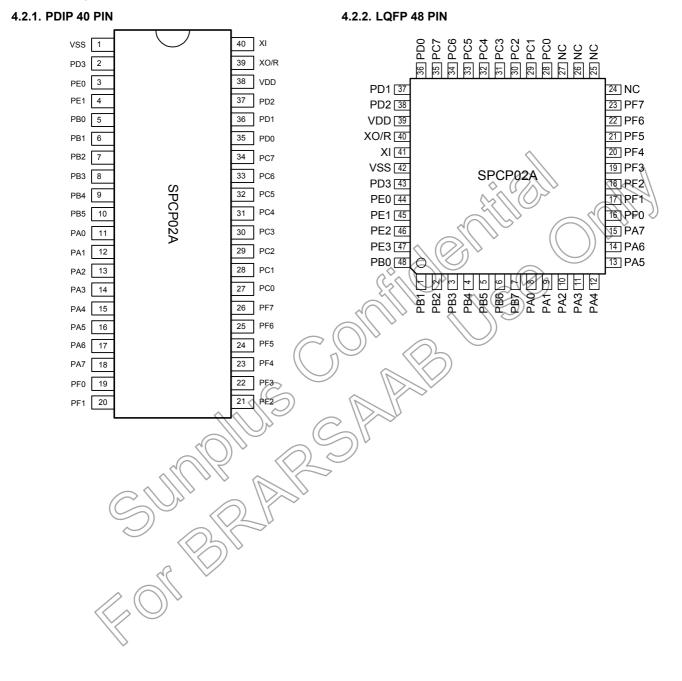

Note: for package type LQFP 48 the followings are NC pin: 24, 25, 26, 27

### 4.1. Ordering Information

| Product Number    | Package Type           |

|-------------------|------------------------|

| SPCP02A-NnnV-C    | Chip form              |

| SPCP02A-NnnV-PD12 | Package form - PDIP 40 |

| SPCP02A-NnnV-PL23 | Package form - LQFP 48 |

**Note1:** Code number is assigned for customer.

**Note2:** Code number (N = A - Z or 0 - 9, nn = 00 - 99); version (V = A - Z).

### SPCP02A

### 4.2. PIN Assignment

### **5. FUNCTIONAL DESCRIPTIONS**

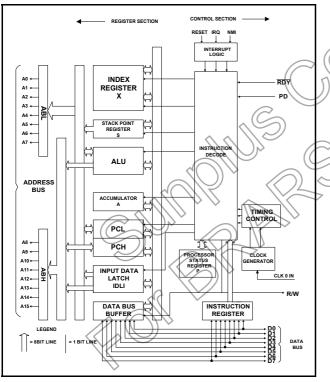

### 5.1. CPU

The microprocessor of SPCP02A is a SUNPLUS high performance processor equipped with Accumulator, Program Counter, X Register, Stack Pointer and Processor Status Register (The same as 6502 instruction structure). SPCP02A is a fully static CMOS design. The oscillation frequency can be run up to 6.0MHz depends on the application needs.

### 5.1.1. Processor status register

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| Flag | Ν | V | - | В | - | I | Z | С |

N: Negative, V: Overflow, B: Brk command, I: IRQ disable, Z: Zero, C: Carry

### 5.1.2. Block diagram of SUNPLUS CPU

### 5.2. Memory

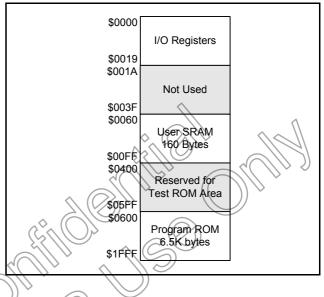

### 5.2.1. Memory map

5.2.2. RAM

Total of 160 bytes of RAM (including the stack) is available from \$0060 to \$00FF. The stack begins at address \$00FF and proceeds down to \$0060.

### 5.2.3. ROM

The 7168 bytes of ROM on chip include 6656 bytes of user ROM (located from \$0600 through \$1FFF) and 512 bytes of internal test ROM (located from \$0400 through \$05FF). User's program can only be allocated from \$0600 through \$1FFF (6.5K).

### 5.2.4. NMI, reset, IRQ vectors

The address of NMI (not provided in this chip), RESET and IRQ are located from \$1FFA to \$1FFF. The interrupt vectors must be specified in the program as follows:

| ORG | \$1FFA      | ; | define SPCP02A chip |

|-----|-------------|---|---------------------|

|     |             | ; | interrupt vector.   |

| DW  | NMI_ROUTINE |   |                     |

| DW  | RESET       |   |                     |

| DW  | INT_ROUTINE |   |                     |

When using emulation board with EPROM (for 27C256), the address of \$7FFA must be defined as follows:

| ORG | \$7ffa      | ; interrupt vector for | - |

|-----|-------------|------------------------|---|

|     |             | ; EPROM with           |   |

| DW  | NMI_ROUTINE | ; Emulation Board.     |   |

| DW  | RESET       |                        |   |

| DW  | INT_ROUTINE |                        |   |

When using emulation board with Sunplus ICE, users fill the ORG address of \$0FFFA as follows:

| ORG | \$0FFFA     | ; interrupt vector for |

|-----|-------------|------------------------|

|     |             | ; SUNPLUS ICE.         |

| DW  | NMI_ROUTINE |                        |

| DW  | RESET       |                        |

| DW  | INT_ROUTINE |                        |

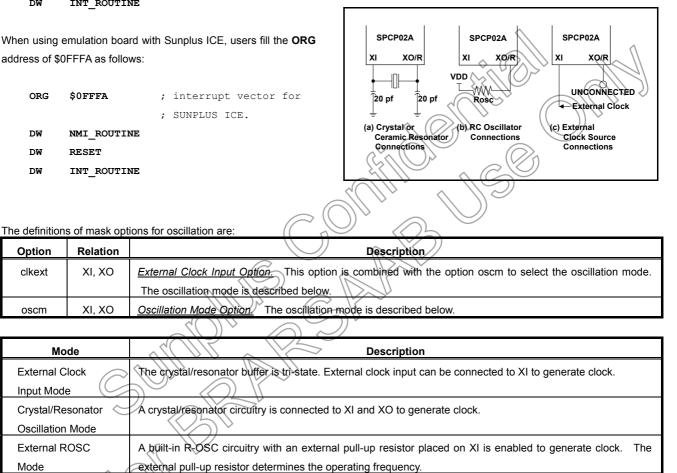

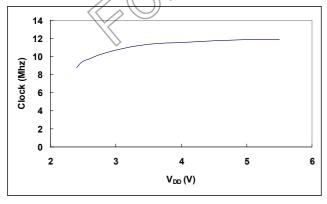

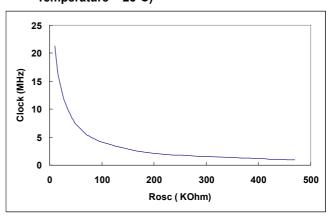

### 5.3. Oscillator

The SPCP02A supports AT-cut parallel resonant oscillated Crystal /Resonator, RC oscillator, or external clock sources by mask option (select one from three types). The design of application circuit should follow the vendor's specifications and recommendations. The diagram listed below represents typical X'TAL/ROSC circuits for most applications:

Option

clkext

oscm

Mode

Mode

Crystal/Resonator Oscillation Mode External ROSC

External Clock Input Mode

Relation

XI, XO

XI, XO

### 5.4. Control Register Summary

The function blocks have two kinds of control input. One is mask option and the other is programmable register. Mask options are used as permanent assignment. They are configured with the program code at the same time. Once the mask options are written to SPCP02A, they are unchangeable as the program code. The mask options are described in later section. Programmable registers control the function blocks by programming. The program can access the registers to achieve specific functions. The registers are summarized as follows. All function registers will be set to "0" (except *rt1* and *rt0* in *TCS1*) when a reset signal is given. The bits *rt1* and *rt0* will be set to "1" when a reset signal occurred.

| Abbr.  | Register                  | bit 7                      | bit 6              | bit 5    | bit 4  | bit 3   | bit 2                             | bit_1                     | bit 0      | Enable                       |

|--------|---------------------------|----------------------------|--------------------|----------|--------|---------|-----------------------------------|---------------------------|------------|------------------------------|

| Addr.  | R/W Control               |                            |                    |          | Defaul | t Value |                                   |                           |            | 1                            |

| PA     | Port A Data               | a7:0                       |                    |          |        |         |                                   |                           |            |                              |

| \$0000 | a a a a a a a a           | 0                          | 0                  | 0        | 0      | 0       | 0                                 |                           | 0          | $\langle \langle    \rangle$ |

| PB     | Port B Data               |                            |                    |          | b7     | 7:0     | $\langle \langle \rangle \rangle$ | 5°                        |            |                              |

| \$0001 | a a a a a a a a           | 0                          | 0                  | 0        | 0      | <0      |                                   | 0                         | ( o ))     | $\checkmark$                 |

| DPA    | Port A Data Direction     | <u> </u>                   |                    |          | dpa    | a7:0    | 9                                 |                           | $\bigcirc$ | 0=IN                         |

| \$0002 | w w w w w w w             | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | $\approx 000$             | (0)        | 1=OUT                        |

| DPB    | Port B Data Direction     |                            |                    |          | dpb    | 0:70    | <u> </u>                          | $\widetilde{\mathcal{D}}$ |            | 0=IN                         |

| \$0003 | w w w w w w w             | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | (0)                       | (0)        | 1=OUT                        |

| TCS1   | Timer Ctl. & Status 1     | tof1                       | rtif               | tofe1    | rtie   | tofr1   | rtifr                             | rt1                       | rt0        |                              |

| \$0004 | r r a a w w a a           | 0                          | 0                  | (( o ))  | 0      | (0)     | ) (0)                             | 1                         | 1          | 1=SET                        |

| TCR1   | Timer Counter Reg. 1      |                            | C                  |          | tm1    | r7:0    |                                   |                           | r          |                              |

| \$0005 | r r r r r r r r           | 0                          | $\left( 0 \right)$ | ) 0      | Pa     | 0       | 0                                 | 0                         | 0          |                              |

| IRQS   | IRQ Control & Status      |                            | irgr               | irqf2    | irge2  | irqf    |                                   |                           | irqe       |                              |

| \$0006 | - w r a r a               | $\langle \bigcirc \rangle$ | (0)                |          | )      | 0       | -                                 | -                         | 0          |                              |

| CPWD   | CMP & WDT Status          |                            |                    |          | /      |         |                                   |                           | wdt        |                              |

| \$0007 | w                         | <u> </u>                   | A                  | <u> </u> | -      | -       | -                                 | -                         | 0          | 1=CLR                        |

| SNW    | Stop & Wait               | $\bigcirc$                 |                    | >`       | stop   |         |                                   |                           |            |                              |

| \$0008 | w                         |                            | Sh                 | -        | (0)    | -       | -                                 | -                         | -          | 1=SET                        |

| RPA    | Port A Pull-up Control    | 251                        |                    |          | rpa    | 7:0     | 1                                 |                           |            | 0=Enable                     |

| \$0009 | wwwwwwww                  | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | (0)                       | (0)        | 1=Disable                    |

| RPB    | Port B Pull-up Control    | -                          |                    |          | rpb    | 7:0     | i                                 | r                         | r          | 0=Enable                     |

| \$000A | w w w w w w w             | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | (0)                       | (0)        | 1=Disable                    |

| RPC    | Port C Pull-up Control    | i                          |                    |          | rpc    | 7:0     | i                                 | r                         | r          | 0=Enable                     |

| \$000B | w w w w w w w w           | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | (0)                       | (0)        | 1=Disable                    |

| PC     | Port C Data               |                            |                    |          | c7     | 7:0     |                                   |                           |            |                              |

| \$000C | a a a a a a a a           | 0                          | 0                  | 0        | 0      | 0       | 0                                 | 0                         | 0          |                              |

| DPC    | Port C Data Direction     | I                          |                    |          | dpo    | :0      | 1                                 |                           |            | 0=IN                         |

|        | w w w w w w w w           | (0)                        | (0)                | (0)      | (0)    | (0)     | (0)                               | (0)                       | (0)        | 1=OUT                        |

| DPD    | Port D Data Direction     | iadr                       | oper               | ssr1     | ssr0   | dpd3    | dpd2                              | dpd1                      | dpd0       | 0=IN                         |

| \$0011 | r r r r w w w w           | 0                          | 0                  | 0        | 0      | (0)     | (0)                               | (0)                       | (0)        | 1=OUT                        |

| PD     | Port D Data               |                            |                    | ssr1     | ssr0   | d3      | d2                                | d1                        | d0         |                              |

| \$0012 | w w a a a a               | -                          | -                  | (0)      | (0)    | 0       | 0                                 | 0                         | 0          |                              |

| RPD    | Port D Pull-up Control    |                            |                    |          |        | rpd3    | rpd2                              | rpd1                      | rpd0       | 0=Enable                     |

| \$0013 | -   -   -   w   w   w   w | -                          | -                  | -        | -      | (0)     | (0)                               | (0)                       | (0)        | 1=Disable                    |

| DPE    | Port E Data Direction     |                            |                    |          |        | dpe3    | dpe2                              | dpe1                      | dpe0       | 0=IN                         |

| \$0014 | w w w w                   | -                          | -                  | -        | -      | (0)     | (0)                               | (0)                       | (0)        | 1=OUT                        |

© Sunplus Technology Co., Ltd. Proprietary & Confidential

| Abbr.  | Register                 | bit 7 | bit 6 | bit 5 | bit 4 | bit 3       | bit 2 | bit 1             | bit 0  | Enable    |

|--------|--------------------------|-------|-------|-------|-------|-------------|-------|-------------------|--------|-----------|

| Addr.  | R/W Control              |       |       | -     | Defau | t Value     |       |                   |        |           |

| PE     | Port E Data              |       |       |       |       | e3          | e2    | e1                | e0     |           |

| \$0015 | a a a a                  | -     | -     | -     | -     | 0           | 0     | 0                 | 0      |           |

| RPE    | Port E Pull-up/down Ctl. |       |       |       |       | rpe3        | rpe2  | rpe1              | rpe0   | 0=Enable  |

| \$0016 | w w w w                  | -     | -     | -     | -     | (0)         | (0)   | (0)               | (0)    | 1=Disable |

| DPF    | Port F Data Direction    |       | -     |       | dp    | f7:0        |       |                   | -      | 0=IN      |

| \$0017 | w w w w w w w w          | (0)   | (0)   | (0)   | (0)   | (0)         | (0)   | (0)               | (0)    | 1=OUT     |

| PF     | Port F Data              |       |       |       | f7    | <b>7</b> :0 |       | $\langle \rangle$ |        |           |

| \$0018 | a a a a a a a a          | 0     | 0     | 0     | 0     | 0           | 0     | 0                 | 0      | . 1       |

| RPF    | Port F Pull-up Control   |       |       |       | rpf   | 7:0         |       |                   |        | 0=Enable  |

| \$0019 | w w w w w w w w          | (0)   | (0)   | (0)   | (0)   | (0)         | (0)   | (0)               | (0) ~( | 1=Disable |

The value in parentheses () is the power-on default value. The gray blocks are reserved.

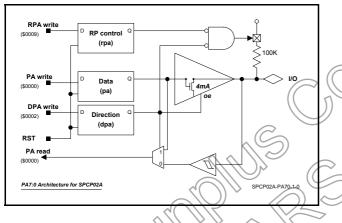

### 5.5. Port A Group

The I/O port A has eight programmable I/Os that are controlled by data register (PA), direction control register (DPA), and pull-up resistance control register (RPA). DPA controls the pad I/O attribute. Setting the bit(s) to "1" will enforce the corresponding pad(s) to output mode. It is a write-only register. PA stores the data contents for output. Reading PA will get the stored data when corresponding bit of DPA is set as output mode; or will get the pad status if it is in input mode.

There is a built-in pull-up resistor on each I/O pin. These pull-up resistors can be controlled by user's program through RPA. When the corresponding control bit  $(rpa_n)$  is enabled, the resistor will be activated in input mode. Each I/O channel has Schmitt-Trigger input buffer for input mode. PA7:0 are open-drain outputs in output mode. Setting the direction bit  $(dpa_n)$  to "1" with the corresponding data bit  $(a_n)$  to "0" will activate the pad as low. Once the data bit is changed to "1", the I/O pad will become tri-state.

The corresponding pads are assigned for SPCP02A as follows (VDD = 5.0V)

| PIN |       | Rp             | IN              | Ουτ   | Special Function |

|-----|-------|----------------|-----------------|-------|------------------|

| PA7 | 100K  | Pull-up @ rpa7 | Schmitt-Trigger | -/4mA | -                |

| PA6 | 100K  | Pull-up @ rpa6 | Schmitt-Trigger | -/4mA | -                |

| PA5 | 100K_ | Pull-up @ rpa5 | Schmitt-Trigger | -/4mA | -                |

| PA4 | 100K  | Pull-up @ rpa4 | Schmitt-Trigger | -/4mA | -                |

| PA3 | 100K  | Pull-up @ rpa3 | Schmitt-Trigger | -/4mA | -                |

| PA2 | 100K  | Pull-up @ rpa2 | Schmitt-Trigger | -/4mA | -                |

| PA1 | 100K  | Pull-up @ rpa1 | Schmitt-Trigger | -/4mA | -                |

| PA0 | 100K  | Pull-up @ rpa0 | Schmitt-Trigger | -/4mA | -                |

The definitions of registers PA, DPA, and RPA are showed below:

| PA   |     | Port A Data Register \$0000 |     |                                                                                                    |  |  |  |  |  |  |  |

|------|-----|-----------------------------|-----|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Name | Bit | RW                          | Dft | Functional Description                                                                             |  |  |  |  |  |  |  |

| a7:0 | 7:0 | А                           | 0h  | Port A Data. When Port A is programmed as output, the output data on Port A pins are determined by |  |  |  |  |  |  |  |

|      |     |                             |     | PA data register. When Port A is programmed as input, any "read" command on Port A will reflect    |  |  |  |  |  |  |  |

|      |     |                             |     | the logic status of those I/O pins. PA data register will be set to "0" when RESET occurred.       |  |  |  |  |  |  |  |

| DPA    |     | Port A Data Direction Register |     |                                                                                           |          |  |  |  |  |  |

|--------|-----|--------------------------------|-----|-------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| Name   | Bit | RW                             | Dft | Functional Description                                                                    |          |  |  |  |  |  |

| dpa7:0 | 7:0 | W                              | 0h  | Port A Data Direction. Port A can be programmed as inputs or outputs by DPA register      | er. When |  |  |  |  |  |

|        |     |                                |     | dpan="1", the corresponding pins are programmed as outputs. When dpan="0", the correspond |          |  |  |  |  |  |

|        |     |                                |     | pins are programmed as inputs. The DPA will be set to "0"(input) when RESET occurred.     |          |  |  |  |  |  |

| RPA    |     | Port A Pull-up Control Register |     |                                                                                                                                                                                                                                                                                          |            |  |  |

|--------|-----|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Name   | Bit | RW                              | Dft | Functional Description                                                                                                                                                                                                                                                                   |            |  |  |

| rpa7:0 | 7:0 | W                               | 0h  | <u>Port A Pull-up Disable</u> . When the bit is "0" the built in pull-up resistor of the corresponding input mode will be enabled. When it is "1", the pull-up resistor will be disabled. The resistors are invalid during output mode. The RPA will be set to "0" (enable mode) by RESE | ne putt-up |  |  |

The I/O structure of Port A is shown below:

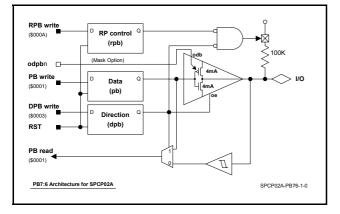

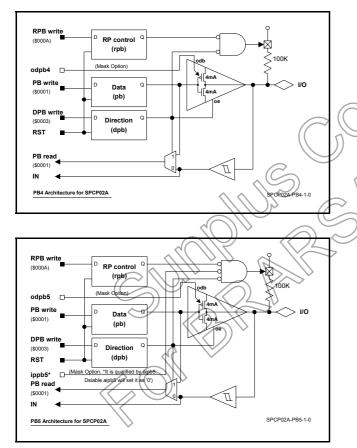

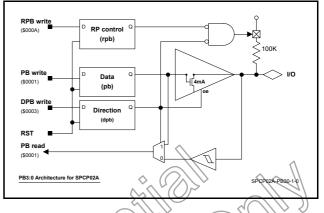

### 5.6. Port B Group

The I/O Port B has 8 programmable I/Os that are controlled by data register (PB), direction control register (DPB), and pull-up resistance control register (RPB). DPB controls the pad I/O attribute. Setting the bit(s) to "1" will enforce the corresponding pad(s) to output mode. It is a write-only register. PB is able to store the data contents for output. Reading PB will get the stored data when corresponding bit of DPB is set as output mode, or will get the pad status if it is in input mode.

There is a built-in pull-up resistor on each I/O channel. These pull-up resistors can be controlled by user's program through RPB. When the corresponding control bit,  $(rpb_n)$  is enabled, the resistor will be activated in input mode. In case of PB5 interrupt input is

enabled by mask option, the pull-up resistor on PB5 is controlled by the mask option of interrupt polarity. Setting rising-edge trigger interrupt on PB5 will disable the pull-up resistor on PB5. If it is configured as falling-edge trigger interrupt input, the resistor on PB5 can be controlled by the bit rpb5 of register RPB.

Each I/O pin has Schmitt-Trigger input buffer for input mode. PB3:0 are open-drain outputs in output mode. Setting the direction bit (dpb<sub>n</sub>,) to "1" with the corresponding data bit, (b<sub>n</sub>,) to "0" will activate the pad as low. Once the data bit is changed to "1" the I/O pad will become tri-state. PB7:4 can be selected as open-drain outputs or totem-pole outputs by mask options. Once the outputs of PB7:4 are set as totem-pole outputs, the only difference to the open-drain outputs is setting dpb<sub>n</sub> to "1" and pb<sub>n</sub>, to "1". In this case, the I/O pin will output high.

PB5 can be external interrupt input with falling-edge trigger by enabling the mask option. More details are described in *Interrupt Chapter*. PB4 can be used as external active-low reset input through mask option.

In 40 pin package, PB7:6 are not present. The values of the correlated data bits or control bits should be kept as the reset default.

### The corresponding pads are assigned for SPCP02A as follows (VDD = 5.0V):

| PIN               |                   | Rp             | IN              | OUT     | Special Function      |

|-------------------|-------------------|----------------|-----------------|---------|-----------------------|

| PB7               | 100K              | Pull-up @ rpb7 | Schmitt-Trigger | (4)/4mA | -                     |

| PB6               | 100K              | Pull-up @ rpb6 | Schmitt-Trigger | (4)/4mA | -                     |

| PB5               | 100K              | Pull-up @ rpb5 | Schmitt-Trigger | (4)/4mA | IRQ0 interrupt input  |

| PB4               | 100K              | Pull-up @ rpb4 | Schmitt-Trigger | (4)/4mA | External nRESET input |

| PB3               | 100K              | Pull-up @ rpb3 | Schmitt-Trigger | -/4mA   | -                     |

| PB2               | 100K              | Pull-up @ rpb2 | Schmitt-Trigger | -/4mA   | -                     |

| PB1               | 100K              | Pull-up @ rpb1 | Schmitt-Trigger | -/4mA   | -                     |

| PB0               | 100K              | Pull-up @ rpb0 | Schmitt-Trigger | -/4mA   | - 1                   |

| he definitions of | of mask options f | or Port B are: |                 |         |                       |

| Option  | Relation | Description                                                                                            |               |

|---------|----------|--------------------------------------------------------------------------------------------------------|---------------|

| aipb5   | PB5      | Alternative Input Option on PB5 for IRQ0. Enable or Disable                                            | •             |

| ippb5   | PB5      | Polarity Control Option on PB5 for IRQ0. Low active or failing edge trigger, or High active o trigger. | r rising edge |

| aipb4   | PB4      | Alternative Input Option on PB5 for IRQ0. Enable or Disable.                                           |               |

| odpb7:4 | PB7:4    | Open-Drain Output Option on PB7:4. Open-drain output or Totem-pole output.                             |               |

### The definitions of registers PB, DPB, and RPB are showed below:

| RW Dft | Functional Description                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                                                                                                                                                                                             |

| A 0    | Port B Data. When Port B is programmed as output, the output data on Port B pin are determined by PB data register. When Port B is programmed as input any "read" command on Port B Data Register will reflect the logic status of those I/O pins. PB data register will be set to "0" when RESET occurred. |

|        | A 0                                                                                                                                                                                                                                                                                                         |

| DPB    |     | )<br>2   | ノ          | Port B Data Direction Register                                                                                                                                            | \$0003   |

|--------|-----|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Name   | Bit | RW       | Dft        | Functional Description                                                                                                                                                    |          |

| dpb7:0 | 7:0 | w        | 0          | Port B Data Direction. Port B can be programmed as inputs or outputs by DPB registe                                                                                       |          |

|        |     | $\sim ($ | $\bigcirc$ | dpbn="1", the corresponding pins are programmed as outputs. When dpbn="0", the correpins are programmed as inputs. The DPB will be set to "0"(input) when RESET occurred. | sponding |

| RPB    |     | ÷. |     | Port B Pull-up Control Register \$000A                                                                 |

|--------|-----|----|-----|--------------------------------------------------------------------------------------------------------|

| Name   | Bit | RW | Dft | Functional Description                                                                                 |

| rpb7:0 | 7:0 | W  | 0h  | Port B Pull-up Disable. When the bit is "0", the built in pull-up resistor of the corresponding pin in |

|        |     |    |     | input mode will be enabled. When it is "1", the pull-up resistor will be disabled. The pull-up         |

|        |     |    |     | resistors are invalid during output mode. The RPB will be set to "0" (enable mode) by RESET.           |

The I/O structures of Port B are shown below:

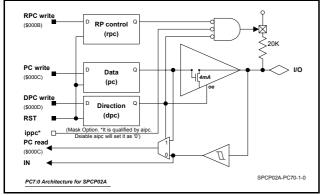

### 5.7. Port C Group

The I/O Port C has 8 programmable I/Os that are controlled by data register (PC), direction control register (DPC), and pull-up resistance control register (RPC). DPC controls the pad I/O attribute. Setting the bit(s) to "1" will enforce the corresponding pad(s) to output mode. It is a write-only register. PC stores the data contents for output. Reading PC will get the stored data when corresponding bit of DPC is set as output mode, or will get the pad status if it is in input mode.

There is a built-in pull-up resistor on each I/O pin. These pull-up resistors can be controlled by user's program through RPC. When the corresponding control bit  $(rpc_n)$  is enabled, the resistor will be active in input mode. In case of group interrupt input is set by mask option, the pull-up resistors on Port C are controlled by the mask option of interrupt polarity. Setting rising-edge trigger interrupt on PC7:0 will disable all pull-up resistors. If PC7:0 are configured as falling-edge trigger interrupt inputs, the resistors on PC7:0 can be controlled by the register RPC.

Each I/O pin has Schmitt-Trigger input buffer for input mode. PC7:0 are open-drain outputs in output mode. Setting the direction bit  $(dpc_n)$  to "1" with the corresponding data bit  $(c_n)$  to "0" will activate the pad as low. Once the data bit is changed to "1", the I/O pad will become tri-state.

PC7:0 are utilized as external interrupt inputs. More details will be described in *Interrupt Chapter*.

### The pad assignment for SPCP02A is as follows (VDD = 5.0V):

| PIN |     | Rp             | IN              | OUT   | Special Function     |

|-----|-----|----------------|-----------------|-------|----------------------|

| PC7 | 20K | Pull-up @ rpc7 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC6 | 20K | Pull-up @ rpc6 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC5 | 20K | Pull-up @ rpc5 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC4 | 20K | Pull-up @ rpc4 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC3 | 20K | Pull-up @ rpc3 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC2 | 20K | Pull-up @ rpc2 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC1 | 20K | Pull-up @ rpc1 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

| PC0 | 20K | Pull-up @ rpc0 | Schmitt-Trigger | -/4mA | IRQ2 interrupt input |

The definitions of mask options for Port C are:

| Option | Relation | Description                                                                                                 |

|--------|----------|-------------------------------------------------------------------------------------------------------------|

| aipc   | PC7:0    | Alternative Input Option on PC for IRQ2. Disable or Enable.                                                 |

| ippc   | PC7:0    | Polarity Control Option of Interrupt Input on Port C. Active Low or Falling Edge Trigger, or Active High or |

|        |          | Rising Edge Trigger.                                                                                        |

|        |          | 10/11 × 11/2)                                                                                               |

### The definitions of registers PC, DPC, and RPC are showed below:

| PC   |     |    |     | Port C Data Register \$000C                                                                                                                                                                                                                                                                                              |  |  |  |

|------|-----|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name | Bit | RW | Dft | Functional Description                                                                                                                                                                                                                                                                                                   |  |  |  |

| c7:0 | 7:0 | A  | 0h  | <u>Port C Data</u> . When Port C is programmed as output, the output data on Port C pins are determined<br>by PC data register. When Port C is programmed as input, any "read" command on Port C Data<br>Register will reflect the logic status of I/O pins. PC data register will be set to "0" when RESET<br>occurred. |  |  |  |

|      |     |    |     |                                                                                                                                                                                                                                                                                                                          |  |  |  |

|           | Port C Data Direction Register                                                                                                                                                                                                                                          | \$000D                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| it RW Dft | Functional Description                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

| :0 W Oh   | Port C Data Direction. Port C can be programmed as inputs or outputs by DPC register dpcn="1", the corresponding pins are programmed as outputs. When dpcn="0", the corresponding pins are programmed as inputs. The DPC will be set to "0"(input) when RESET occurred. |                                                                                                                                                                                  |

|           |                                                                                                                                                                                                                                                                         | 0 W 0h Port-C Data Direction. Port C can be programmed as inputs or outputs by DPC register dpcn="1", the corresponding pins are programmed as outputs. When dpcn="0", the corre |

|        |     | 2 ((       |            | $\diamond$                                                                                   |            |

|--------|-----|------------|------------|----------------------------------------------------------------------------------------------|------------|

| RPC    |     | $\nearrow$ | $\bigcirc$ | Port C Pull-up Control Register                                                              | \$000B     |

| Name   | Bit | RW         | Dft        | Functional Description                                                                       |            |

| rpc7:0 | 7:0 | W          | 0h         | Port C Pull-up Disable. When the bit is "0", the built in pull-up resistor of the correspond | 0.         |

|        |     |            |            | input mode will be enabled. When it is "1", the pull-up resistor will be disabled. The       | ne pull-up |

|        |     |            |            | resistors are invalid during output mode. The RPC will be set to "0" (enable mode) by RESE   | ET.        |

### SPCP02A

#### The I/O structure of Port C is shown below:

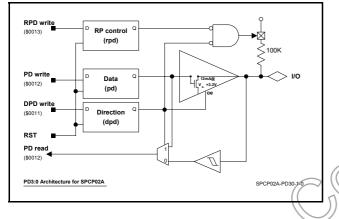

### 5.8. Port D Group

The I/O Port D has 4 programmable I/Os that are controlled by data register (PD), direction control register (DPD), and pull-up resistance control register (RPD). DPD controls the pad I/O

The pad assignment for SPCP02A is as follows (VDD = 5.0V):

attribute. Setting the bit(s) to "1" will enforce the corresponding pad(s) to output mode. It is a write-only register. PD stores the data contents for output. Reading PD will get the stored data when corresponding bit of DPD is set as output mode, or will get the pad status if it is in input mode.

There is a built-in pull-up resistor on each I/O pin. These pull-up resistors can be controlled by user's program through RPD. When the corresponding control bit (rpd<sub>n</sub>,) is enabled, the resistor will be activated in input mode. Each I/O pin has Schmitt-Trigger input buffer for input mode. PD3:0 are open-drain outputs in output mode. Setting the direction bit (dpd<sub>n</sub>) to "1" with the corresponding data bit (d<sub>n</sub>) to "0" will activate the pad as low. Once the data bit is changed to "1", the I/O pad will become tri-state. The output of PD can be used as LED sink output.

| PIN | Rp             |                 | OUT                 | Special Function  |

|-----|----------------|-----------------|---------------------|-------------------|

| PD3 | 100K Up @ rpd3 | Schmitt-Trigger | -/12mA @ Vol = 3.2V | nLED3 sink output |

| PD2 | 100K Up @ rpd2 | Schmitt-Trigger | /12mA @ VoL = 3.2V  | nLED2 sink output |

| PD1 | 100K Up @ rpd1 | Schmitt-Trigger | -/12mA @ Vo∟ = 3.2V | nLED1 sink output |

| PD0 | 100K Up @ rpd0 | Schmitt-Trigger | -/12mA @ VoL = 3.2V | nLED0 sink output |

The definitions of registers PD, DPD, and RPD are showed below:

| PD    | <          | Port D Data Register \$0012                                                                        |

|-------|------------|----------------------------------------------------------------------------------------------------|

| Name  | Bit RW Dft | Functional Description                                                                             |

| resv. | 7:6 -))    | Reserved.                                                                                          |

|       | 5:4 W      | Refer to Section Specific Shadow Register for more information.                                    |

| d3:0  | 3:0 A 0h   | Port D Data. When Port D in programmed as output, the output data on Port A pins are determined    |

|       | - C        | by PD data register. When Port D is programmed as input, any "read" command on Port D Data         |

|       |            | Register will reflect the logic status of I/O pins. PD data register will be set to "0" when RESET |

|       |            | occurred.                                                                                          |

| DPD    |     | Port D Data Direction Register \$0011 |     |                                                                                                                                                                                                                 |  |  |  |

|--------|-----|---------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name   | Bit | RW                                    | Dft | Functional Description                                                                                                                                                                                          |  |  |  |

|        | 7:4 | R                                     | 0h  | Refer to Section Reset for more information.                                                                                                                                                                    |  |  |  |

| dpd3:0 | 3:0 | W                                     | 0h  | <u>Port D Data Direction</u> . Port D can be programmed as inputs or outputs by DPD register. When <b>dpd</b> n="1", the corresponding pins are programmed as outputs. When <b>dpd</b> n="0", the corresponding |  |  |  |

|        |     |                                       |     | pins are programmed as inputs. The DPD will be set to "0" (input) when RESET occurred.                                                                                                                          |  |  |  |

| RPD    |     | Port D Pull-up Register \$0013 |     |                                                                                                        |  |  |  |

|--------|-----|--------------------------------|-----|--------------------------------------------------------------------------------------------------------|--|--|--|

| Name   | Bit | RW                             | Dft | Functional Description                                                                                 |  |  |  |

| resv.  | 7:4 | -                              |     | Reserved.                                                                                              |  |  |  |

| rpd3:0 | 3:0 | W                              | 0h  | Port D Pull-up Disable. When the bit is "0", the built in pull-up resistor of the corresponding pin in |  |  |  |

|        |     |                                |     | input mode will be enabled. When it is "1", the pull-up resistor will be disabled. The pull-up         |  |  |  |

|        |     |                                |     | resistors are invalid during output mode. The RPD will be set to "0" (enable mode) by RESET.           |  |  |  |

The I/O structure of Port D is shown below:

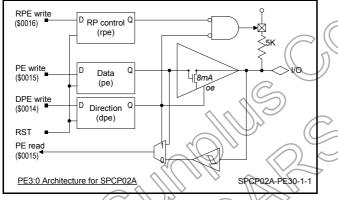

### 5.9. Port E Group

The I/O Port E has 4 programmable I/Os that are controlled by data register (PE,) direction control register (DPE), and pull-up/down resistance control register (RPE). DPE controls the pad I/O attribute. Setting the bit(s) to "1" will enforce the

corresponding pad(s) to output mode. It is a write-only register. PE stores the data contents for output. Reading PE will get the stored data when corresponding bit of DPE is set as output mode, or will get the pad status if it is in nput mode.

There is a built-in pull-up resistor on each pad) These pull-up resistors can be controlled by user's program through RPE. When the corresponding control bit ( $rpe_n$ ) is enabled, the resistor will be activated in input mode. Each I/O pin has Schmitt-Trigger input buffer for input mode. PE3:0 are open-drain outputs in output mode. Setting the direction bit (dpe\_n.) to "1" with the corresponding data bit (e\_n.) to "0" will activate the pad as low. Once the data bit is changed to "1", the I/O pad will become tri-state.

In 40-pin package, PE3:2 are not present. The values of the correlated data bits or control bits must be kept as the reset default.

### The pad assignment for SPCP02A is as follows (VDD = 5.0V):

| PIN | Rp           |                 | OUT   | Special Function |

|-----|--------------|-----------------|-------|------------------|

| PE3 | 5K Up @ rpa3 | Schmitt-Trigger | -/8mA | -                |

| PE2 | 5K Up @ rpa2 | Schmitt-Trigger | -/8mA | -                |

| PE1 | 5K Up @ rpa1 | Schmitt-Trigger | -/8mA | -                |

| PE0 | 5K Up @ rpa0 | Schmitt-Trigger | -/8mA | -                |

The definitions of registers PE, DPE, and RPE are shown below:

| PE    |     | Port E Data Register \$0015      |    |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-------|-----|----------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name  | Bit | it RW Dft Functional Description |    |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| resv. | 7:4 | -                                |    | Reserved.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| e3:0  | 3:0 | A                                | 0h | <u>Port E Data</u> . When Port E is programmed as output pins, the output data on Port A pins are determined by PE data register. When Port E is programmed as input pins, any "read" command on Port E Data Register will reflect the logic status of those I/O pins. PE data register will be set to "0" when RESET occurred. |  |  |  |

| DPE    |     | Port E Data Direction Register \$0014 |     |                                                                                                                                                                                                                                                                                               |  |  |  |

|--------|-----|---------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name   | Bit | RW                                    | Dft | Functional Description                                                                                                                                                                                                                                                                        |  |  |  |

| resv.  | 7:4 | -                                     |     | Reserved.                                                                                                                                                                                                                                                                                     |  |  |  |

| dpe3:0 | 3:0 | W                                     | 0h  | <u>Port E Data Direction</u> . Port E can be programmed as inputs or outputs by DPE regist <b>dpen=</b> "1", the corresponding pins are programmed as outputs. When <b>dpen=</b> "0", the corresponding pins are programmed as inputs. The DPE will be set to "0"(input) when RESET occurred. |  |  |  |

| RPE    |     | Port E Pull-up/down Register \$0016 |     |                                                                                                                                                                         |  |  |  |

|--------|-----|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name   | Bit | RW                                  | Dft | Functional Description                                                                                                                                                  |  |  |  |

| resv.  | 7:4 | -                                   |     | Reserved.                                                                                                                                                               |  |  |  |

| rpe3:0 | 3:0 | W                                   | 0h  | Port E Pull-u Disable. When the bit is "0", the built in pull-up resistor of the corresponding pin in input                                                             |  |  |  |

|        |     |                                     |     | mode will be enabled. When it is "1", the resistor will be disabled. The resistors are invalid during<br>output mode. The RPE will be set to "0"(enable mode) by RESET. |  |  |  |

The I/O structure of Port E is shown below:

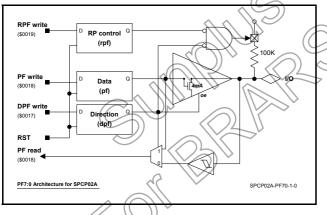

### 5.10. Port F Group

The I/O Port F has 8 programmable I/Os that are controlled by data register (PF), direction control register (DPF), and pull-up/down resistance control register (RPF). DPF controls the

The pad assignment for SPCP02A is as follows (VDD = 5.0V:)

pad I/O attribute. Setting the bit(s) to "1" will enforce the corresponding pad(s) to output mode. It is a write-only register. PF stores the data contents for output. Reading PF will get the stored data when corresponding bit of DPF is set as output mode, or will get the pad status if it is in input mode.

There is a built-in pull-up resistor on each I/O channel. These pull-up resistors can be controlled by users' program through RPF. When the corresponding control bit  $(rpf_n)$  is enabled, the resistor will be activated in input mode. Each I/O pin has Schmitt-Trigger input buffer for input mode. PF7:0 are open-drain outputs in output mode. Setting the direction bit  $(dpf_n)$  to "1" with the corresponding data bit  $(f_n)$  to "0" will activate the pad as low. Once the data bit is changed to "1", the I/O pad will become tri-state.

| PIN | Rp             | IN              | OUT   | Special Function |

|-----|----------------|-----------------|-------|------------------|

| PF7 | 100K Up @ rpa7 | Schmitt-Trigger | -/4mA | -                |

| PF6 | 100K Up @ rpa6 | Schmitt-Trigger | -/4mA | -                |

| PF5 | 100K Up @ rpa5 | Schmitt-Trigger | -/4mA | -                |

| PF4 | 100K Up @ rpa4 | Schmitt-Trigger | -/4mA | -                |

| PF3 | 100K Up @ rpa3 | Schmitt-Trigger | -/4mA | -                |

| PF2 | 100K Up @ rpa2 | Schmitt-Trigger | -/4mA | -                |

| PF1 | 100K Up @ rpa1 | Schmitt-Trigger | -/4mA | -                |

| PF0 | 100K Up @ rpa0 | Schmitt-Trigger | -/4mA | -                |

#### The definitions of registers PF, DPF, and RPF are shown below:

| PF   |     | Port F Data Register \$0018   |    |                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------|-----|-------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name | Bit | RW Dft Functional Description |    |                                                                                                                                                                                                                                                                                                                           |  |  |  |

| f7:0 | 7:0 | A                             | 0h | <u>Port F Data</u> . When Port F is programmed as output pins, the output data on Port F pins are determined by PF data register. When Port F is programmed as input pins, any "read" command on Port F Data Register will reflect the logic status of I/O pins. PF data register will be set to "0" when RESET occurred. |  |  |  |

| DPF    |     | Port F Data Direction Register A \$0017 |     |                                                                                                                                                                                                                                                                                                       |  |  |

|--------|-----|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name   | Bit | RW                                      | Dft | Functional Description                                                                                                                                                                                                                                                                                |  |  |

| dpf7:0 | 7:0 | W                                       | 0h  | <u>Port F Data Direction</u> . Port F can be programmed as inputs or outputs by DPF register. When <b>dpf</b> n="1", the corresponding pins are programmed as outputs. When <b>dpf</b> n="0", the corresponding pins are programmed as inputs. The DPF will be set to "0"(input) when RESET occurred. |  |  |

|        |     |                                         |     | pins are programmed as inputs. The DTT will be set to orthout when REOLT becarted                                                                                                                                                                                                                     |  |  |

| RPF    |     | Port F Pull-up Control Register \$0019 |     |                                                                                                        |  |  |  |  |

|--------|-----|----------------------------------------|-----|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name   | Bit | RW                                     | Dft | Functional Description                                                                                 |  |  |  |  |

| rpf7:0 | 7:0 | W                                      | 0h  | Port F Pull-up Disable. When the bit is "0", the built in pull-up resistor of the corresponding pin in |  |  |  |  |

|        |     |                                        |     | input mode will be enabled. When it is "1", the pull-up resistor will be disabled. The pull-up         |  |  |  |  |

|        |     |                                        |     | resistors are invalid during output mode. The RPF will be set to "0" (enable mode) by RESET.           |  |  |  |  |

The I/O structure of Port F is shown below:

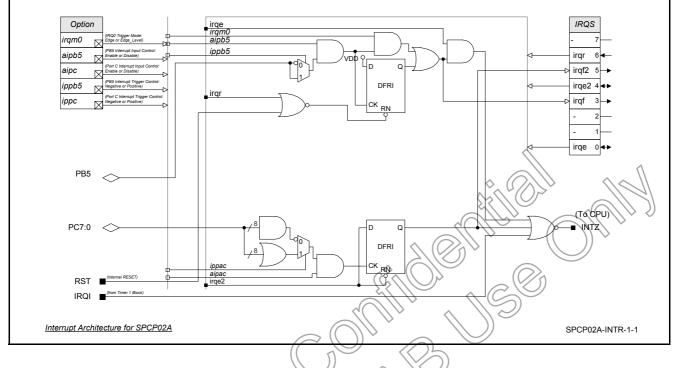

### 5.11. Interrupt

There are four types of interrupts: Software Interrupt, External Interrupt, Timer Interrupt, and Comparator interrupt. The last three interrupts has individual status (occurred or not occurred) and control (enable or not enabled) registers. In contrast. software interrupt does not have these control registers. In general, once an interrupt event occurs, the corresponding flag bit will be set. If the related interrupt control bit is enabled, an interrupt request signal will be generated and be executed by CPU. The interrupt flag bits must be cleared in the interrupt service routine to avoid program from deadlock in interrupt service routine.

Software interrupt is generated by the instruction BRK. The BRK is an executable instruction interrupt; it is executed regardless of the state of the I-bit in the Processor Status Register Flag (inside CPU). The program jumps to interrupt routine immediately when BRK occurred. With any instruction, interrupts pending during the previous instruction is served.

External interrupts come from IRQ0 or IRQ2. These IRQ signals are combined with the mask options and status/control registers to generate the interrupt events to CPU. IRQ0 has an interrupt control bit (irge) to enable the interrupt generating, a write-only clear bit (irqr) to clear occurred event status, and a read-only flag bit (irgf) for get event status. Once an external interrupt is occurred, irqf will be set and it stays set unless the irqr is set to "1" by user's program. When setting irge to enable IRQ0, an interrupt request signal will be generated as long as irgf is set. IRQ2 has only one interrupt control bit (irqe2) and one flag bit (irqf2). Clearing irqe2 will disable the IRQ2. IRQ0 has mask option used in setting the trigger mode of the interrupt event. The trigger mode of IRQ0 can be selected as either edge trigger mode or level trigger mode. On the other hand, IRQ2 only has edge trigger mode. When the interrupt channel is enabled with edge trigger mode, an active transition edge on the external interrupt inputs will generate the interrupt. If the channel is enabled with level trigger mode, the active level of the external interrupt inputs will set the interrupt event until the active level condition is removed. However, user's program must set related irgrn bit to

clear the interrupt occurrence in the interrupt service routine.

In SPCP02A, IRQ0 comes from PB5, and IRQ2 comes from external interrupt group input, PC7:0. Each IRQ channel has a mask option for input control of the interrupt, and a mask option for interrupt polarity. The mask options of input control activates the interrupt input on PB5 or PC7:0. For interrupt polarity, the mask options can be set as rising-edge trigger or falling-edge trigger for the IRQ channels.

When the interrupt input is enabled by the mask option, the control of pull-up resistor(s) will be affected by the mask option of interrupt polarity in case of the option is set as rising-edge trigger (or active high trigger). If the interrupt polarity is set as rising-edge trigger (or active high trigger), the pull-up resistor(s) will be disabled permanently.

The Timer 1 interrupt and the Comparator interrupt will be described in section Timer1 & Real Time Interrupt and section Comparator.

The definitions of mask options for external interrupts are:

|        |          | ions for external interrupts are.                                                                                 |

|--------|----------|-------------------------------------------------------------------------------------------------------------------|

| Option | Relation | Description                                                                                                       |

| irqm0  | IRQ0     | IRQ Trigger Mode Option on IRQ0. Edge Trigger or Level-Edge Trigger.                                              |

| aipb5  | IRQ0,    | Alternative Input Option on PB5 for IRQ0. Alternative input is disabled or enabled. The polarity control          |

|        | PB5      | function of ippb5 is ignored when aipb5 is disabled. At controls the input PB5 for IRQ0.                          |

| aipc   | IRQ2,    | Alternative Input Option on PC for IRQ2. Alternative Input is disabled or enabled. The polarity control           |

|        | PC7:0    | function of ippc is ignored when aipc is disabled. It controls the group input PC7:0 for IRQ2.                    |

| ippb5  | IRQ0,    | Polarity Control Option of Interrupt Input on PB5. Falling edge trigger or rising edge trigger. It controls the   |

|        | PB5      | polarity of interrupt input on PB5. When aipb5 is disabled, this option is ignored. When it is effective with     |

|        |          | value '1', the internal Pull-up Resistor on PB5 is disabled.                                                      |

| іррс   | IRQ2,    | Polarity Control Option of Interrupt Input on PC. Falling edge trigger or rising edge trigger. It controls the    |

|        | PC7:0    | polarity of interrupt input on PC and it does affect the pull-up/down resistors on all PC pins when the           |

|        |          | alternative input is enabled by aipc. If the option is set '1', all PC pull-up resistors are disabled. In case of |

|        |          | setting this bit to "0", the resistors are not affected by the option.                                            |

### The control register for external interrupt inputs is defined in detail as below:

| IRQS  | (   | $C_{\epsilon}$ | 2   | IRQ Control & Status Register \$000                                                                                                                                                                                                                                                                            | 6  |

|-------|-----|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Name  | Bit | RW             | Dft | Functional Description                                                                                                                                                                                                                                                                                         |    |

| resv. | 7   | -              |     | Reserved                                                                                                                                                                                                                                                                                                       |    |

| irqr  | 6   | W              | Â   | Irgf Clear bit. It clears flag irqf. Writing "1" to irqr will clear flag irqf. 0: not clear, 1: clear irqf.                                                                                                                                                                                                    |    |

| irqf2 | 5   | R              | ð   | Interrupt Flag bit of IRQ2 Input. It indicates the interrupt requests coming from channel IRQ2. The flag is set by the interrupt events and is cleared by setting <b>irqe2</b> to "0". The IRQ2 is from PC7:0. (In no interrupt, 1: interrupt requested.                                                       |    |

| irqe2 | 4   | A              | 0   | <u>Interrupt Control bit of IRQ2 Input</u> . It controls whether the interrupt requests comes from IRQ2. (<br>disable, 1: enable.                                                                                                                                                                              | 0: |

| irqf  | 3   | R              | 0   | <u>Interrupt Flag bit of IRQ0 Input</u> . It is the flag of interrupt requests coming from channel IRQ0. The flag is set by the interrupt events and is cleared by setting <b>irqr</b> to "1". Setting <b>irqe</b> does not affect <b>irqf</b> . IRQ0 comes from PB5. 0: no interrupt, 1: interrupt requested. | -  |

| resv. | 2:1 | -              |     | Reserved.                                                                                                                                                                                                                                                                                                      |    |

| irqe  | 0   | А              | 0   | Interrupt Control bit of IRQ0 Input. It controls whether the interrupt requests comes from IRQ0. (<br>disable, 1: enable.                                                                                                                                                                                      | 0: |

#### The interrupt source diagrams in different emulation modes are shown below:

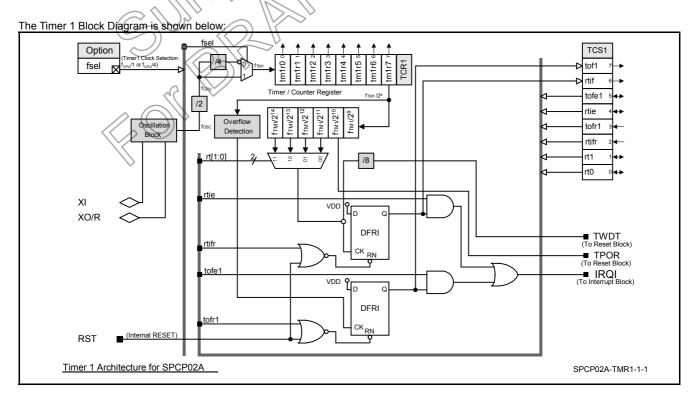

### 5.12. Timer1 & Real Time Interrupt

The clock input (XI/XO/R pins),  $f_{OSC}$ , is internally divided by two to generate the CPU clock ( $f_{CPU}$ ) for entire system. Timer 1 clock ( $f_{TM1}$ ) comes from CPU clock with the division of 1 or 4, configured by mask option. The timer clock is fed into an 8-bit free-run timer built as Timer 1 function. Timer 1 Count Register (TCR1) reads the current counting value of Timer 1. Once TCR1 overflows, it will set the interrupt flag bit tof1 of Timer 1 Countol & Status Register (TCS1) to "1" and will generate interrupt for service if the interrupt enable bit (tofe1) of TCS1 is set. Writing the write-only bit (tofr1) of TCS1 with "1" clears the flag.

The additional counting stages perform the Real Time Interrupt (RTI) function for timing applications, the watchdog Timer for function recovery, and the Power On Reset (POR) cycle for lowing

clock during power up. More information about the POR and WDT functions are described in *WDT & Reset Chapter*.

Real Time Interrupt (RTI) comes from the additional counting stages. Some of these additional counting stages consist of a pre-scalar to perform the periodic timing events. The timing events will set the flag bit (**rtif**) in TCS1 and will generate interrupt for service if the interrupt enable bit (**rtie**) of TCS1 is set. Writing the write-only bit (**rtifr**) of TCS1 with "1" clears the flag. The rt1 and rt0 of TCS1 select the division for pre-scalar. The corresponding definitions are described as follows.

| The definition of mask option for Timer1 & Real Time Interrupt | is: |

|----------------------------------------------------------------|-----|

|----------------------------------------------------------------|-----|

| Option | Relation | Description                                                     |